IIC (Inter-Integrated Circuit) là giao diện ghép nối nối tiếp bán song công (half-duplex) dạng buýt được tích hợp trong nhiều thiết bị như cảm biến, đồng hồ thời gian thực RTC và bộ nhớ EEPROM. IIC cũng được gọi là I2C hoặc I2C trong nhiều tài liệu kỹ thuật. Buýt I2C được khởi xướng ban đầu bởi hãng Philips, nhưng trong những năm gần đây đã trở thành một chuẩn ghép nối được sử dụng rộng rãi bởi nhiều công ty bán dẫn. I2C là lý tưởng để gắn các thiết bị ngoại vi tốc độ thấp vào bo mạch chủ hoặc hệ thống nhúng hoặc bất cứ ứng dụng nào cần giao tiếp đáng tin cậy trong một khoảng cách ngắn. Như chúng ta sẽ thấy trong chương này, I2C cung cấp một quá trình truyền thông định hướng kết nối. Nhiều thiết bị có thể được kết nối với bus I2C chỉ bằng hai dây. Đặc tả về giao thức I2C đinh nghĩa nhiều tốc độ buýt, bao gồm chế độ tiêu chuẩn ở tốc độ 100 kbps (Kilo bit mỗi giây), chế độ nhanh ở tốc độ 400 kbps, chế độ nhanh tăng cường (fast-plus) ở tốc độ 1 Mbps (Mega bit mỗi giây) và chế độ tốc độ cao ở mức 3,33 Mbps. Mỗi thiết bị truyền thông có thể hoạt động ở một trong hai vai trò, vai trò thiết bị chủ hoặc vai trò thiết bị phục vụ. Trong đó, thiết bị chủ có quyền khởi tạo một phiên truyền thông với một thiết bị phục vụ. Hơn thế, một thiết bị có thể chuyển đổi giữa vai trò thiết bị chủ và vai trò thiết bị phục vụ, làm cho bus I2C thực sự là giao diện bus nối tiếp đa thiết bị chủ. Dữ liệu có thể được nhận hoặc gửi đến thiết bị phục vụ.

Trong bài viết này, chúng ta xem xét các cấu trúc của bus I2C và tập trung vào các thuật ngữ và giao thức làm việc của buýt I2C.

NỘI DUNG

1. Kết nối trên buýt I2C

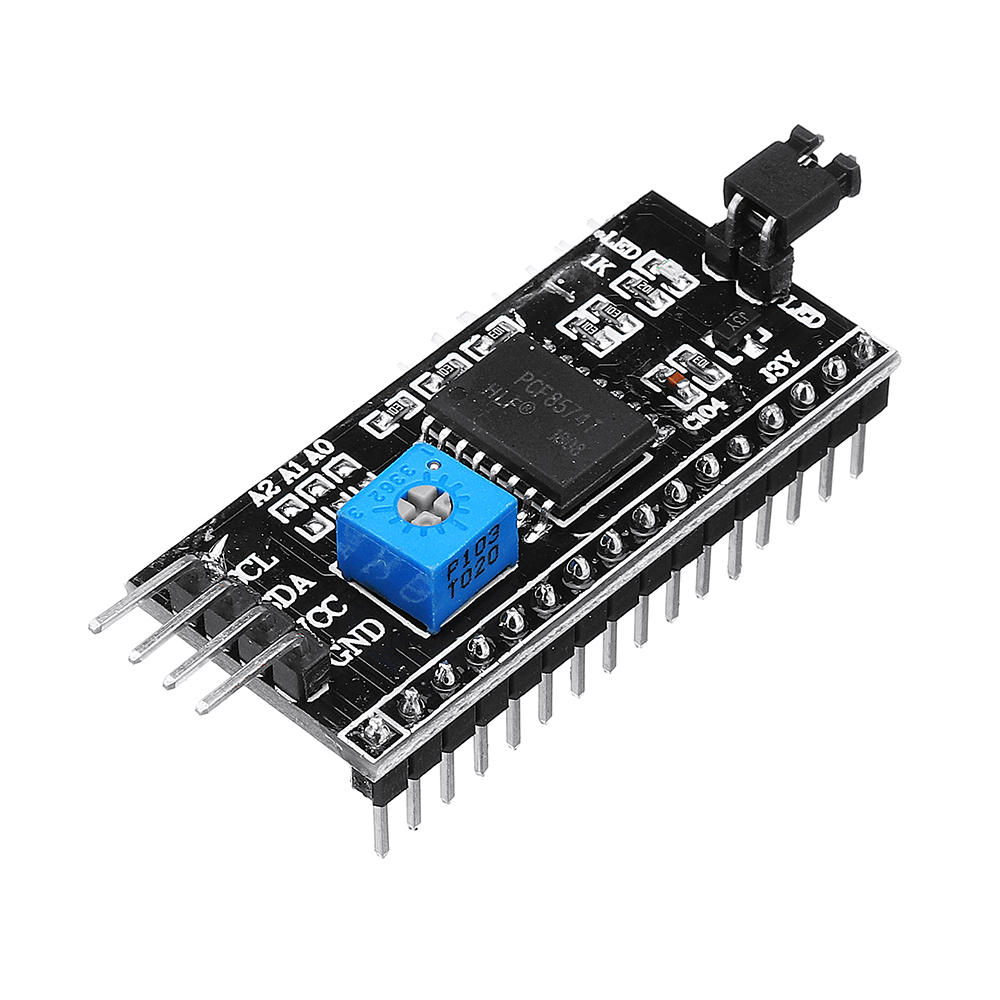

I2C là một giao thức bus nối tiếp đa thiết bị chủ sử dụng hai đường tín hiệu. Điều này có nghĩa là các thiết bị I2C chỉ sử dụng 2 chân để truyền dữ liệu thay vì 8 chân trở lên như trong các buýt song song truyền thống. Hai tín hiệu này bao gồm tín hiệu SCL (Serial clock) dùng để đồng bộ hóa việc truyền dữ liệu giữa hai chip và SDA (Serial Data) như chỉ ra trong Hình 8‑1. Việc giảm các chân truyền thông như vậy làm giảm kích thước linh kiện và mức tiêu thụ năng lượng đáng kể, khiến chúng trở nên lý tưởng cho nhiều ứng dụng. Vì chỉ sử dụng hai chân, SDA và SCK, cho truyền thông nên trong một số tài liệu I2C còn được gọi là Giao diện nối tiếp hai dây (TWI: Two-Wire Serial Interface).

Hình 8‑1. Mô hình kết nối các thiết bị tới buýt I2C.

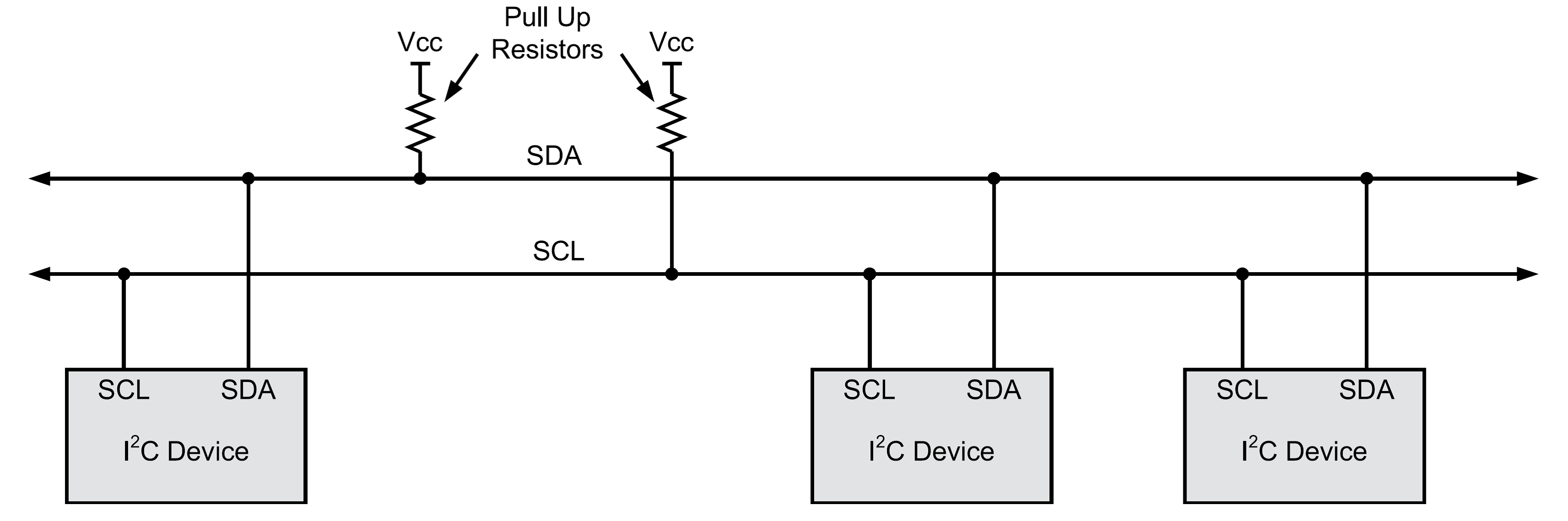

Các thiết bị I2C sử dụng 2 chân truyền dẫn hai chiều có cấu hình cực máng hở như Hình 8‑2 để truyền dữ liệu. Do đó để thực hiện I2C, nó là cần thiết phải mắc một điện trở kéo lên 4,7k ohm cho mỗi đường buýt. Kết nối như vậy cho phép thực hiện một mạch logic AND giữa các chân trên tất cả các thiết bị được kết nối vào buýt I2C. Điều đó có nghĩa là nếu một hoặc nhiều thiết bị kéo đường buýt xuống mức thấp, trạng thái đường buýt sẽ ở mức logic 0. Mức logic trên một đường buýt chỉ là 1 nếu không có thiết bị nào kéo đường này xuống mức thấp.

Hình 8‑2. Mạch điều khiển các chân SDA và SCL trong các thiết bị I2C [20].

Các mức logic thấp và cao trên một đường buýt được tạo ra về mặt vật lý bằng cách kéo đường đó xuống đất hoặc giải phóng đường đó. Về mặt hiệu dụng, một thiết bị được kết nối với bus I2C chỉ có thể điều khiển một đường buýt tới mức logic thấp. Tất cả các thiết bị được kết nối với bus I2C phải lắng nghe buýt liên tục. Một thiết bị chủ dự định khởi tạo một phiên truyền thông trên buýt I2C, khi phát hiện điều kiện START sẽ đợi cho đến khi một điều kiện STOP được phát hiện trước khi thử truy cập lại buýt. Tương tự, các thiết bị phục vụ trên bus I2C sẽ khớp địa chỉ của nó với địa chỉ nhận được trên buýt sau điều kiện START để xác định xem chúng có phải là thiết bị được dự định để truyền dữ liệu hay không. Một thiết bị phục vụ không được định địa chỉ phải chờ điều kiện STOP trước khi lắng nghe lại buýt.

2. Các nút trên buýt I2C

Trong giao thức I2C, hơn 100 thiết bị có thể chia sẻ một bus I2C chung. Mỗi thiết bị này được gọi là một nút. Trong giao thức I2C, mỗi nút có thể hoạt động như một thiết bị chủ chủ (master) hoặc thiết bị phục vụ (Slave). Master là một thiết bị tạo tín hiệu xung nhịp cho hệ thống, nó cũng khởi tạo và chấm dứt một phiên truyền thông trên buýt. Slave là một nút nhận tín hiệu xung nhịp và được định địa chỉ bởi Master. Trong I2C, cả Master và Slave đều có thể nhận hoặc truyền dữ liệu. Vì vậy, có 4 chế độ hoạt động cho mỗi nút đó là: bộ phát master, bộ thu master, bộ phát slave và bộ thu slave. Lưu ý rằng mỗi nút có thể có nhiều chế độ hoạt động tại các thời điểm khác nhau nhưng nó chỉ có một chế độ hoạt động tại một thời điểm nhất định. Ví dụ, trong hệ thống ghép nối vi điều khiển với bộ nhớ EEPROM thông qua buýt I2C, vi điều khiển là thiết bị chủ có thể thực hiện chức năng bộ phát để viết dữ liệu tới bộ nhớ EEPROM ở một thời điểm và thực hiện chức năng bộ nhận khi đọc dữ liệu từ EEPROM ở một thời điểm khác. Trong các phần tiếp theo, chúng ta sẽ thấy một nút có thể thực hiện chức năng của một thiết bị chủ và thiết bị phục vụ vào các thời điểm khác nhau.

Mỗi thiết bị được kết nối với bus I2C sẽ được gán một địa chỉ duy nhất. Địa chỉ này được sử dụng bởi thiết bị chủ để liên lạc với một thiết bị phục vụ cụ thể. Dưới đây liệt kê các thuộc tính quan trọng liên quan đến giao thức bus I2C:

- Mỗi thiết bị phục vụ được gán một địa chỉ duy nhất 7-bit.

- Hai đường tín hiệu, SCL và SDA, là hai chiều.

- Dữ liệu được truyền dưới dạng một chuỗi các byte 8-bit.

- Ngoài việc truyền dữ liệu, cặp đường truyền SDA và SCL cũng được dùng để truyền đi các tín hiệu điều khiển bao gồm điều kiện START/STOP (điều kiện bắt đầu/dừng) quá trình truyền thông, điều khiển gửi/nhận dữ liệu cũng như xác nhận (Acknowledgement) và truyền thông địa chỉ của thiết bị phục vụ.

3. Chuỗi báo hiệu cho truyền dữ liệu

Một thiết bị chủ bắt đầu truyền dữ liệu trên bus I2C bằng cách phát đi một điều kiện START. Điều kiện START có thể được coi là một cảnh báo tới tất cả các thiết bị được kết nối với buýt. Sau điều kiện START, thiết bị chính sẽ truyền ĐỊA CHỈ của thiết bị phục vụ theo sau là tín hiệu điều khiển READ/WRITE (R/W). Tín hiệu điều khiển READ/WRITE thông báo cho thiết bị phục vụ biết thiết bị chủ sẽ đọc dữ liệu từ nó hay sẽ viết dữ liệu tới nó. Sau khi nhận được địa chỉ từ buýt, tất cả các thiết bị sẽ so sánh địa chỉ này với địa chỉ của chính chúng. Thiết bị phục vụ có địa chỉ khớp với địa chỉ trên buýt sẽ phản hồi lại bằng tín hiệu xác nhận (ACK). Mặt khác, những thiết bị mà không khớp với địa chỉ trên buýt sẽ tiếp tục chờ cho đến khi buýt ngưng hoạt động sau khi phát đi điều kiện STOP.

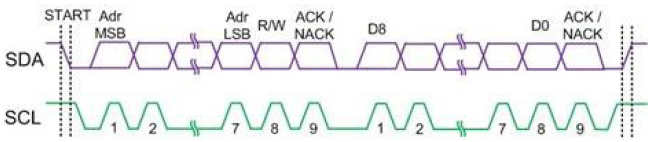

Sau khi nhận được tín hiệu ACK, thiết bị chủ bắt đầu quá trình truyền hoặc nhận dữ liệu tùy thuộc vào tín hiệu điều khiển R/W được phát sau địa chỉ. Trong trường hợp viết (WRITE), thiết bị chủ sẽ truyền một byte dữ liệu tại một thời điểm và thiết bị phục vụ sẽ phản hồi với tín hiệu ACK sau khi nhận được mỗi byte dữ liệu như trong Hình 8‑3(a). Khi thiết bị chủ kết thúc quá trình truyền dữ liệu nó sẽ tạo ra một điều kiện STOP. Trong trường hợp đọc (READ) dữ liệu, thiết bị phục vụ sẽ gửi byte dữ liệu đầu tiên sau khi gửi tín hiệu ACK. Thiết bị chủ phản hồi với tín hiệu ACK sau khi nhận được một byte dữ liệu như có mô tả trong Hình 8‑3(b). Khi thiết bị chủ đã nhận được đủ dữ liệu nó sẽ gửi tín hiệu NACK theo sau là điều kiện STOP để giải phóng buýt cho các nút khác.

(a) (a) |

(b) |

Hình 8‑3. Giao thức truyền và nhận dữ liệu trên buýt I2C.

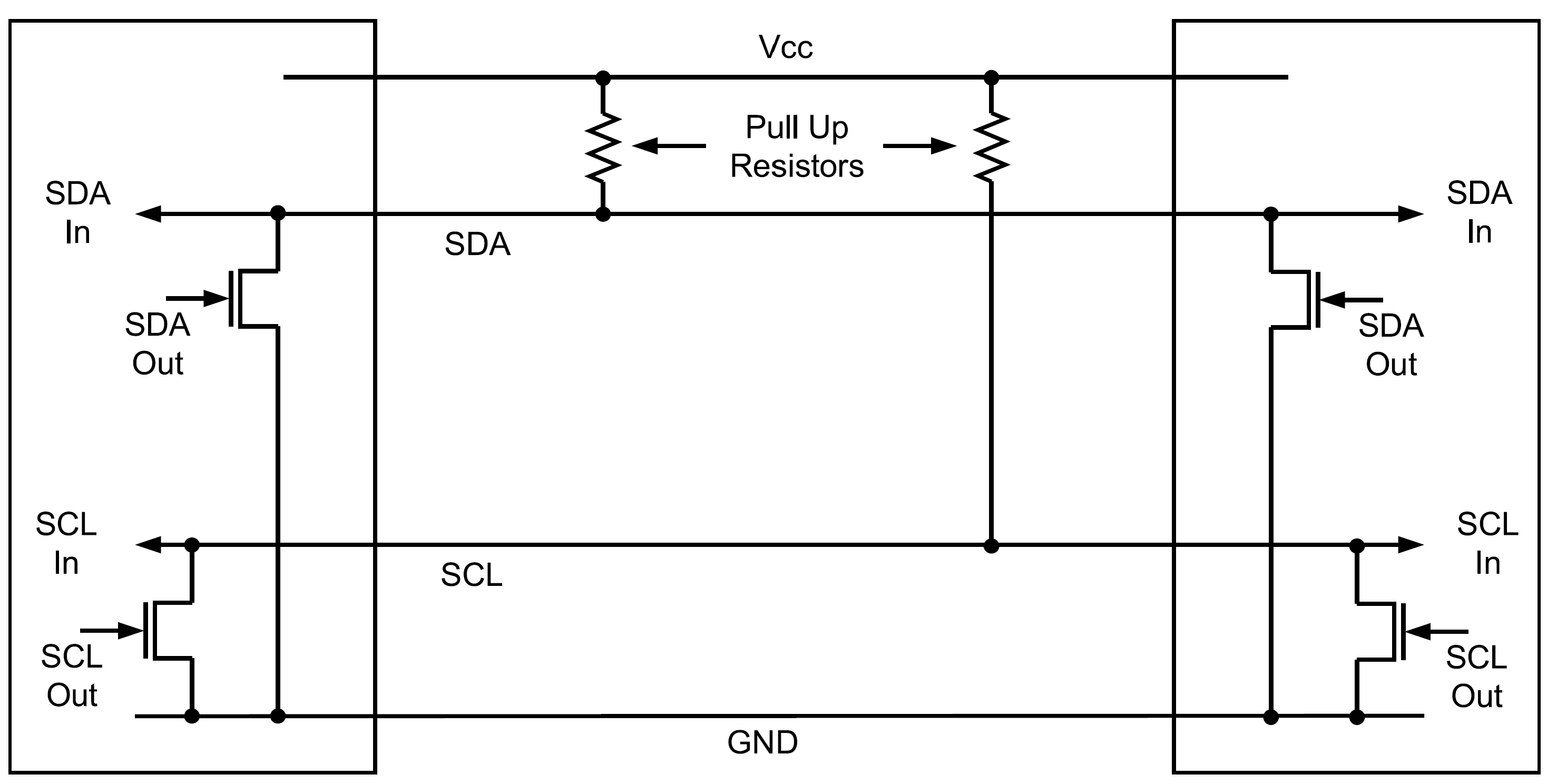

Chuỗi các hoạt động để thực hiện truyền dữ liệu giữa các thiết bị chủ và thiết bị phục vụ có thể được quan sát từ Hình 11.6. Có thể thấy rằng mỗi lần truyền dữ liệu đòi hỏi một chuỗi chín bit bao gồm 8 bit dữ liệu và 1 bit ACK. Sau điều kiện START, byte đầu tiên luôn được truyền bởi thiết bị chủ. Trong đó, 7 bit có ý nghĩa nhất của byte này là địa chỉ của thiết bị phục vụ, trong khi bit ít ý nghĩa nhất của byte này là bit báo hiệu R/W.

Hình 8‑4. Chuỗi các hoạt động để thực hiện truyền và nhận dữ liệu trên buýt I2C.

4. Định dạng bit

I2C là một giao thức truyền thông nối tiếp đồng bộ. Điều này có nghĩa là mỗi bit dữ liệu được truyền trên đường SDA được đồng bộ hóa bởi một xung từ cao đến thấp trên đường SCL. Khi bus I2C không hoạt động, cả hai đường SCL và SDA đều ở trạng thái logic cao. Theo giao thức I2C, đường dữ liệu không thể thay đổi khi đường xung nhịp ở mức cao, nó chỉ có thể thay đổi khi đường xung nhịp ở mức thấp như chỉ ra trong Hình 8‑5. Để truyền dữ liệu hợp lệ đòi hỏi dữ liệu được giữ ổn định trên đường SDA trong khi đường SCL duy trì ở trạng thái cao. Điều kiện STOP và START là ngoại lệ duy nhất cho quy tắc này.

Hình 8‑5. Định dạng một bit trong buýt I2C.

Như chúng ta đã đề cập trước đây, I2C là một giao thức truyền thông hướng kết nối, điều đó có nghĩa là mỗi lần truyền được bắt đầu bởi một điều kiện START và được kết thúc bởi một điều kiện STOP. Cũng nhớ rằng các điều kiện START và STOP luôn được tạo bởi thiết bị chủ.

Các điều kiện STOP và START phải được phân biệt với các bit của địa chỉ hoặc dữ liệu và đó là lý do tại sao chúng không tuân theo quy tắc định dạng bit mà chúng ta đã đề cập trước đó.

Các điều kiện START và STOP được tạo bằng cách giữ đường SCL ở mức cao và sau đó thay đổi mức logic trên đường SDA. Điều kiện START được tạo ra bởi sự thay đổi từ mức cao xuống mức thấp trên đường SDA khi giữ SCL ở mức cao. Điều kiện STOP được tạo bởi sự thay đổi từ mức thấp lên mức cao trên đường SDA khi giữ đường SCL ở mức cao như chỉ ra trong Hình 8‑6.

Hình 8‑6. Các điều kiện START và STOP trong giao thức I2C.

Buýt được coi là ở trạng thái bận giữa mỗi cặp điều kiện START và STOP và không có thiết bị chủ nào khác được phép kiểm soát buýt khi buýt đang bận. Nếu một thiết bị chủ đang có quyền điều khiển buýt muốn tiếp tục khởi tạo một phiên truyền thông mới và không muốn giải phóng buýt trước khi bắt đầu phiên truyền mới, nó sẽ phát ra một điều kiện START mới giữa một cặp điều kiện START và STOP. Nó được gọi là điều kiện REPEATED START hoặc đơn giản là điều kiện RESTART như chỉ ra trong Hình 8‑7.

Hình 8‑7. Điều kiện START lặp lại.

Ví dụ 8‑1 đưa ra một ví dụ cho thấy tại sao điều kiện REPEATED START là cần thiết trong ứng dụng của buýt I2C.

|

Ví dụ 8‑1 |

|

Hãy đưa ra một ví dụ để chỉ ra khi nào thiết bị chủ phải sử dụng điều kiện REPEATED START. Điều gì sẽ xảy ra nếu thiết bị chủ không sử dụng nó? Lời giải: Nếu chúng ta kết nối hai bộ vi điều khiển (µA và µB) và bộ nhớ EEPROM thông qua buýt I2C trong đó µA muốn tính tổng của hai ô nhớ tại địa chỉ 0x34 và 0x35 của EEPROM và hiển thị nó trên LCD, thì chúng ta phải sử dụng điều kiện REPEATED START. Hãy cùng xem những gì có thể xảy ra nếu µA không sử dụng điều kiện REPEATED START. µA truyền điều kiện START và đọc nội dung tại địa chỉ 0x34 của EEPROM và truyền điều kiện STOP để giải phóng buýt. Trước khi µA tiếp tục đọc nội dung tại địa chỉ 0x35, µB chiếm giữ buýt và thay đổi nội dung của các ô nhớ tại địa chỉ 0x34 và 0x35 của bộ nhớ EEPROM. Sau đó µA đọc nội dung của ô nhớ tại địa chỉ 0x35, cộng nó vào nội dung của ô nhớ đã đọc trước đó tại địa chỉ 0x34 và hiển thị kết quả lên LCD. Kết quả trên màn hình LCD lúc này không phải là tổng các giá trị cũ cảu các ô nhơ tại địa chỉ 0x34 và 0x35 cũng không phải là tổng của các giá trị mới của các ô nhơ tại địa chỉ 0x34 và 0x35 của bộ nhớ EEPROM. |

5. Định dạng khung truyền trong I2C

Trong giao thức I2C, mỗi địa chỉ hoặc dữ liệu được truyền phải được đóng thành khung có độ dài 9 bit. Tám bit đầu tiên được đặt lên đường SDA bởi bên phát và bit thứ 9 là bit xác nhận ACK (Acknowledge) hoặc NACK (Negative Acknowledge) của bên nhận. Lưu ý rằng tín hiệu xung nhịp luôn được tạo bởi thiết bị chủ bất kể nó là bên phát hay bên thu. Để cho phép bên thu đưa ra bit xác nhận, bên phát phải giải phóng đường SDA trong xung nhịp thứ 9 để bên nhận có thể kéo dòng SDA xuống thấp để chỉ ra ACK như chỉ ra trong hình 9-5. Nếu bên nhận không kéo dòng SDA xuống thấp, nó được coi là NACK.

Hình 8‑8. Định dạng một byte trong buýt I2C.

Trong giao thức I2C, mỗi byte có thể chứa địa chỉ hoặc dữ liệu. Cũng lưu ý rằng: Điều kiện START + byte địa chỉ thiết bị phục vụ + một hoặc nhiều byte dữ liệu + điều kiện STOP cùng nhau tạo thành một khung truyền dữ liệu hoàn chỉnh. Tiếp theo chúng ta sẽ nghiên cứu các định dạng của địa chỉ thiết bị phục vụ và byte dữ liệu và cách kết hợp chúng để tạo ra một khung truyền hoàn chỉnh.

6. Định dạng Byte địa chỉ

Tất cả các byte địa chỉ được truyền trên bus I2C đều có độ dài chín bit. Nó bao gồm bảy bit địa chỉ, một bit điều khiển đọc/viết (READ/WRITE) và một bit xác nhận ACK (Acknowledge) như chỉ ra trong hình 9-6.

Hình 8‑9. Định dạng địa chỉ trong giao thức I2C.

Các bit địa chỉ được sử dụng để định địa chỉ cho một thiết bị phục vụ cụ thể trên buýt. Địa chỉ 7 bit cho phép thiết bị chủ định địa chỉ tối đa 128 thiết bị phục vụ trên buýt. Trong đó, địa chỉ “0000 000” được dành riêng cho cuộc gọi quảng bá và tất cả địa chỉ có định dạng “1111 xxx” được dành riêng cho một số thiết bị đặc biệt. Ngoài ra còn có 8 địa chỉ dành riêng khác. Điều đó có nghĩa là chỉ có (128-1-8-8) địa chỉ có thể dùng cho các thiết bị của người dùng. Trong bus I2C, bit có có ý nghĩa nhất MSB của địa chỉ được truyền trước tiên. Bus I2C cũng hỗ trợ chế độ địa chỉ 10 bit trong đó địa chỉ được chia thành hai khung khi bắt đầu truyền. Đối với phần còn lại của bài viết, chúng ta sẽ chỉ tập trung vào chế độ địa chỉ 7 bit.

Bit thứ 8 trong byte địa chỉ là bit điều khiển READ/WRITE. Nếu bit này được đặt, master sẽ đọc từ Slave bằng byte tiếp theo trên buýt, ngược lại master sẽ ghi byte tiếp theo trên bus vào Slave. Khi một thiết bị Slave phát hiện địa chỉ của nó trên xe buýt, nó biết rằng nó đang được truy cập và nó phải xác nhận điều đó trong chu kỳ đồng hồ thứ chín bằng cách kéo đường SDA xuống mức thấp. Nếu thiết bị Slave được định địa chỉ chưa sẵn sàng hoặc vì bất kỳ lý do nào không muốn phản hồi thiết bị chủ, nó sẽ để đường SDA ở mức cao trong chu kỳ xung nhịp thứ 9. Điều kiện này được coi là NACK. Trong trường hợp NACK, thiết bị chủ có thể truyền điều kiện STOP để chấm dứt phiên truyền hoặc điều kiện REPETED START để bắt đầu phiên truyền mới.

Ví dụ 8‑2 cho thấy cách mà một thiết bị chủ báo hiệu rằng nó muốn viết tới một thiết bị phục vụ.

|

Ví dụ 8‑2 |

|

Chỉ ra cách một thiết bị chủ khởi tạo một hoạt động viết tới một thiết bị phục vụ có địa chỉ “1001101”? Lời giải: Các hành động sau đây phải được thực hiện bởi thiết bị chủ: 1) Thiết bị chủ đặt một chuyển tiếp từ cao xuống thấp trên đường SDA trong khi giữ SCL ở mức cao để tạo ra một điều kiện START để bắt đầu phiên truyền thông; 2) Thiết bị chủ truyền “1001101 0” vào buýt. Trong đó, bảy bit đầu tiên “1001101” biểu thị địa chỉ thiết bị phục vụ và bit thứ 8 có giá trị “0” biểu thị thao tác Ghi và thiết bị chủ sẽ ghi byte (dữ liệu) tiếp theo vào thiết bị phục vụ. |

Một byte địa chỉ bao gồm một địa chỉ thiết bị phục vụ và bit chọn chế độ READ được gọi là SLA + R trong khi một byte địa chỉ bao gồm một địa chỉ thiết bị phục vụ và bit chọn chế độ WRITE được gọi là SLA + W.

Như đã đề cập trước đây, địa chỉ 0000 000 được dành riêng cho cuộc gọi quảng bá. Điều đó có nghĩa là khi một thiết bị chủ truyền đi địa chỉ “0000 000”, tất cả các thiết bị phục vụ đều phải phản hồi bằng cách thay đổi đường SDA thành 0 trong một chu kỳ xung nhịp để xác nhận ACK và chờ để nhận byte dữ liệu. Hoạt động này rất hữu ích khi một thiết bị chủ muốn truyền cùng một byte dữ liệu tới tất cả các thiết bị phục vụ trong hệ thống. Lưu ý rằng địa chỉ cuộc gọi quảng bá không thể được sử dụng để đọc dữ liệu từ thiết bị phục vụ vì buýt không cho phép có nhiều hơn một thiết bị phục vụ có thể ghi vào buýt tại một thời điểm nhất định.

7. Định dạng byte dữ liệu

Giống như các byte khác, byte dữ liệu cũng dài 9 bit. 8 bit đầu tiên là nội dung của byte dữ liệu được truyền và bit thứ 9 dành cho ACK. Nếu bên nhận đã nhận được byte dữ liệu cuối cùng và không muốn nhận thêm dữ liệu, nó có thể đưa ra một báo hiệu NACK bằng cách để đường SDA ở mức cao. Thiết bị chủ nên chấm dứt phiên truyền với điều kiện STOP sau khi NACK xuất hiện. Trong các truyền byte dữ liệu, bit MSB được truyền trước tiên giống như khi truyền địa chỉ.

8. Kết hợp địa chỉ và byte dữ liệu

Trong giao thức I2C, thông thường phiên truyền được bắt đầu bằng điều kiện START, theo sau là byte địa chỉ (SLA + R/W), một hoặc nhiều byte dữ liệu và được kết thúc bằng điều kiện STOP. Hình 8‑10 cho thấy một phiên truyền dữ liệu điển hình.

Hình 8‑10. Giản đồ thời gian một khung truyền hoàn chỉnh.

|

Ví dụ 8‑3 |

|

Chỉ ra cách thiết bị chủ ghi giá trị dữ liệu “1111 0000” vào thiết bị phục vụ có địa chỉ “1001101”? Lời giải: Các hành động sau đây phải được thực hiện bởi thiết bị chủ: 1) Thiết bị chủ tạo ra một chuyển tiếp từ cao xuống thấp trên đường SDA trong khi giữ SCL ở mức cao để tạo ra một điều kiện START cho bắt đầu truyền. 2) Thiết bị chủ truyền chuỗi bit “1001 101 0” trên buýt. Trong đó, bảy bit đầu tiên (“1001 101”) biểu thị địa chỉ của thiết bị phục vụ và bit thứ 8 có giá trị “0” biểu thị thao tác “ghi” và có nghĩa rằng thiết bị chủ sẽ ghi byte (dữ liệu) tiếp theo vào thiết bị phục vụ. 3) Thiết bị phục vụ kéo đường SDA xuống mức thấp ở xung thứ 9 báo hiệu xác nhận ACK để báo rằng nó đã sẵn sàng nhận dữ liệu. 4) Sau khi nhận được xác nhận ACK, thiết bị chủ sẽ truyền byte dữ liệu (“1111 0000”) trên đường SDA với bit MSB truyền đầu tiên. 5) Khi thiết bị phục vụ nhận xong dữ liệu, nó sẽ để đường SDA ở mức cao để báo hiệu NACK thông báo cho thiết bị chủ rằng nó đã nhận được byte dữ liệu cuối cùng và không muốn nhận thêm dữ liệu nữa 6) Sau khi nhận được NACK, thiết bị chủ biết rằng không nên truyền thêm dữ liệu. Thiết bị chủ thay đổi đường SDA khi giữ đường SCL ở mức cao để báo hiệu điều kiện STOP và sau đó giải phóng buýt. |

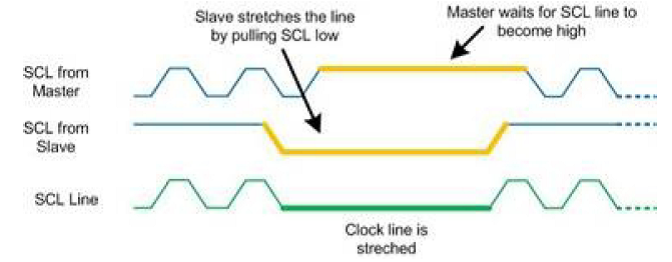

9. Kéo dài xung nhịp

Một trong những tính năng đặc biệt mà giao thức I2C hỗ trợ là tính năng kéo dài xung nhịp. Nó được sử dụng bởi một thiết bị phục vụ tốc độ chậm để đồng bộ hóa với thiết bị chủ. Nếu một thiết bị phục vụ được định địa chỉ không sẵn sàng để xử lý nhiều dữ liệu, nó sẽ kéo dài xung nhịp bằng cách giữ đường xung nhịp SCL ở mức thấp sau khi nhận (hoặc gửi) một bit dữ liệu sao cho thiết bị chủ sẽ không thể nâng đường này lên mức cao (vì các thiết bị được nối dây theo logic AND) và sẽ phải đợi cho đến khi thiết bị phục vụ giải phóng đường SCL để biểu thị nó đã sẵn sàng cho bit tiếp theo như trong Hình 8‑11. Kéo dài xung nhịp có thể được sử dụng để làm chậm xung nhịp cho từng bit hoặc nó có thể được sử dụng để tạm thời dừng xung nhịp ở cuối một byte trong khi bên nhận đang xử lý dữ liệu.

Hình 8‑11. Kéo dài xung nhịp.

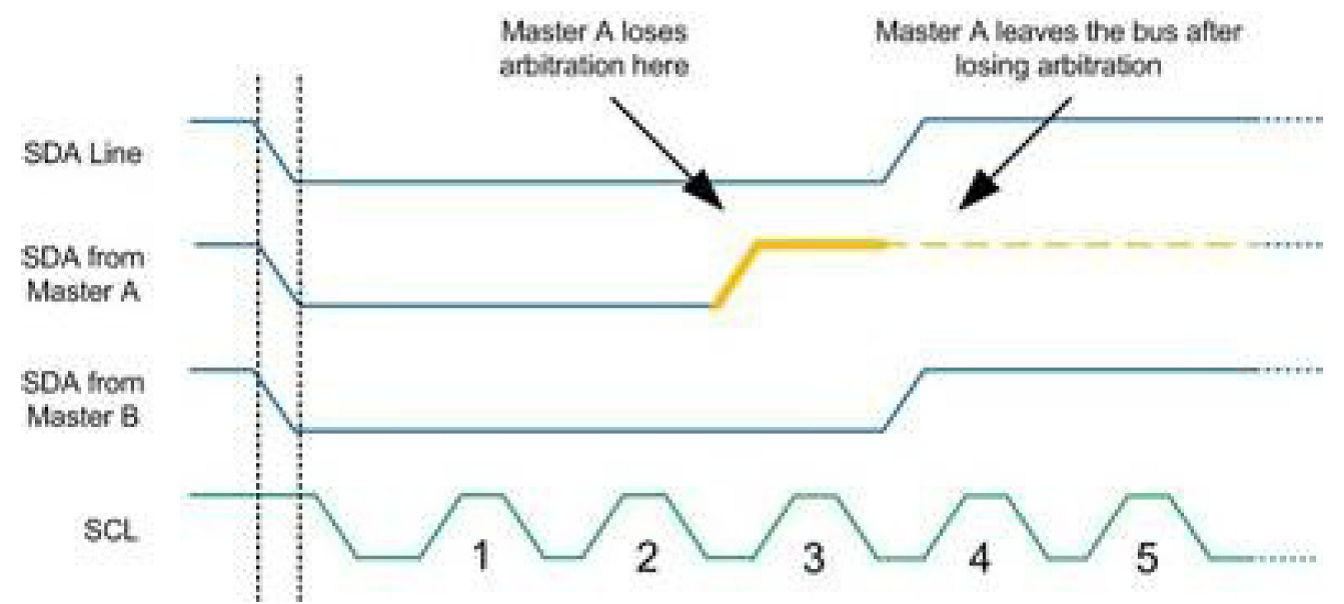

10. Hoạt động trọng tài

Giao thức I2C hỗ trợ hệ thống bus nhiều thiết bị chủ. Nó không có nghĩa là nhiều hơn một thiết bị chủ có thể sử dụng buýt cùng một lúc mà mỗi thiết bị chủ phải chờ cho phiên truyền hiện tại kết thúc mới có thể bắt đầu sử dụng buýt. Tuy nhiên, thực tế có thể xảy ra tình huống có hai hoặc nhiều thiết bị chủ muốn khởi tạo một phiên truyền thông cùng một lúc. Trong trường hợp này hoạt động trọng tài sẽ diễn ra để phân xử xung đột.

Hoạt động trọng tài là quá trình trong đó mỗi thiết bị chủ phải kiểm tra mức logic trên buýt và so sánh với mức logic mà nó đang vận hành buýt [20]. Nếu hai giá trị không khớp nhau, thiết bị chủ đó biết được rằng nó đã mất quyền làm chủ buýt và sẽ phải chuyển sang chế độ của thiết bị phục vụ. Trong hoạt động trọng tài, thiết bị chủ thắng cuộc sẽ tiếp tục truyền dữ liệu trên buýt. Ví dụ 8‑4 sau đây minh họa quá trình trọng tài được thực hiện thế nào.

|

Ví dụ 8‑4 |

|

Nếu hai thiết bị chủ A và B bắt đầu cùng một lúc, điều gì xảy ra nếu thiết bị chủ A muốn viết cho thiết bị phục vụ có địa chỉ “0010 000” và thiết bị chủ B muốn viết cho thiết bị phục vụ có địa chỉ “0001 111”? Lời giải: Hoạt động trọng tài sẽ diễn ra trong quá trình các thiết bị A và B gửi địa chỉ của thiết bị phục vụ mà nó muốn truy xuất lên buýt. Thiết bị chủ A sẽ mất quyền điều khiển buýt trong xung nhịp thứ ba vì giá trị đọc về trên đường SDA là ‘0’ (do thiết bị B phát đi) khác với giá trị “1” mà thiết bị A xuất ra ở xung nhịp thứ ba. Thiết bị A tự chuyển sang chế độ phục vụ và dừng vận hành buýt sau khi mất quyền điều khiển. |

11. Ghi nhiều byte theo loạt

Ghi dữ liệu liên tục theo loạt (Burst) là một phương thức hiệu quả để viết dữ liệu tới các vị trí ô nhớ liên tiếp trong bộ nhớ. Phương thức này được hỗ trợ trong các giao thức buýt I2C, SPI và nhiều giao thức nối tiếp khác. Trong chế độ viết liên tục theo loạt, thiết bị truyền cung cấp địa chỉ của vị trí ô nhớ đầu tiên theo sau là dữ liệu cho vị trí đó. Từ đó trở đi, các byte liên tiếp được ghi vào các vị trí bộ nhớ liên tiếp. Trong chế độ này, thiết bị nhận tự động tăng địa chỉ bên trong nó miễn là không phát hiện thấy điều kiện STOP. Các bước sau đây được sử dụng để gửi (hay ghi) nhiều byte dữ liệu ở chế độ ghi liên tục theo loạt cho các thiết bị I2C.

- Thiết bị chủ tạo ra một điều kiện START.

- Thiết bị chủ truyền địa chỉ thiết bị phục vụ theo sau là một bit ‘0’ (để chọn chế độ ghi).

- Thiết bị chủ truyền địa chỉ bộ nhớ ở vị trí đầu tiên.

- Thiết bị chủ truyền dữ liệu cho vị trí bộ nhớ đầu tiên và từ đó trở đi, thiết bị chủ chỉ đơn giản cung cấp liên tục các byte dữ liệu được đặt vào các vị trí bộ nhớ liên tiếp tiếp theo trong thiết bị phục vụ.

- Thiết bị chủ tạo ra một điều kiện STOP.

Hình 8‑12 cho thấy cách viết 0x05, 0x16 và 0x0B đến 3 vị trí liên tiếp bắt đầu từ vị trí “00001111” của thiết bị phục vụ có địa chỉ “1111000”.

Hình 8‑12. Ví dụ về hoạt động viết dữ liệu theo loạt trên buýt I2C.

12. Đọc nhiều byte theo loạt

Đọc dữ liệu liên tục theo loạt (Burst) là một phương thức hiệu quả để lấy ra nội dung của các vị trí bộ nhớ liên tiếp. Trong chế độ đọc liên tục theo loạt, thiết bị chủ chỉ cung cấp địa chỉ của vị trí ô nhớ đầu tiên. Từ đó trở đi, nội dung từ các vị trí bộ nhớ liên tiếp tiếp theo sẽ được đọc ra tự động. Trong chế độ này, thiết bị phục vụ tự động tăng vị trí địa chỉ bên trong nó miễn là không phát hiện thấy điều kiện STOP. Các bước sau đây được sử dụng để nhận (hay đọc) nhiều byte dữ liệu bằng chế độ truy xuất liên tục theo loạt cho các thiết bị I2C:

- Thiết bị chủ tạo ra một điều kiện START.

- Thiết bị chủ truyền địa chỉ của thiết bị phục vụ theo sau là bit ‘0’ (để chọn chế độ ghi địa chỉ bộ nhớ).

- Thiết bị chủ truyền địa chỉ của vị trí bộ nhớ đầu tiên.

- Thiết bị chủ tạo điều kiện RESTART để chuyển hướng bus từ ghi sang đọc.

- Thiết bị chủ truyền địa chỉ thiết bị phục vụ theo sau là bit ‘1’ (để đọc).

- Thiết bị chủ tạo ra 8 xung trên đường SCL để nhận 8 bit dữ liệu cho vị trí ô nhớ đầu tiên do thiết bị phục vụ cung cấp.

- Thiết bị chủ cung cấp một ACK.

- Thiết bị chủ đọc các vị trí liên tiếp và cung cấp ACK cho mỗi byte.

- Thiết bị chủ đưa ra một NACK cho byte cuối cùng nhận được để báo hiệu cho thiết bị phục vụ rằng việc đọc đã hoàn tất.

- Thiết bị chủ tạo ra một điều kiện STOP.

Hình 8‑13 cho thấy cách đọc ba vị trí liên tiếp bắt đầu từ vị trí “00001111” của thiết bị phục vụ có địa chỉ “1111000”.

Hình 8‑13. Ví dụ về hoạt động đọc dữ liệu theo loạt trên buýt I2C

thanks so much this useful knowledge