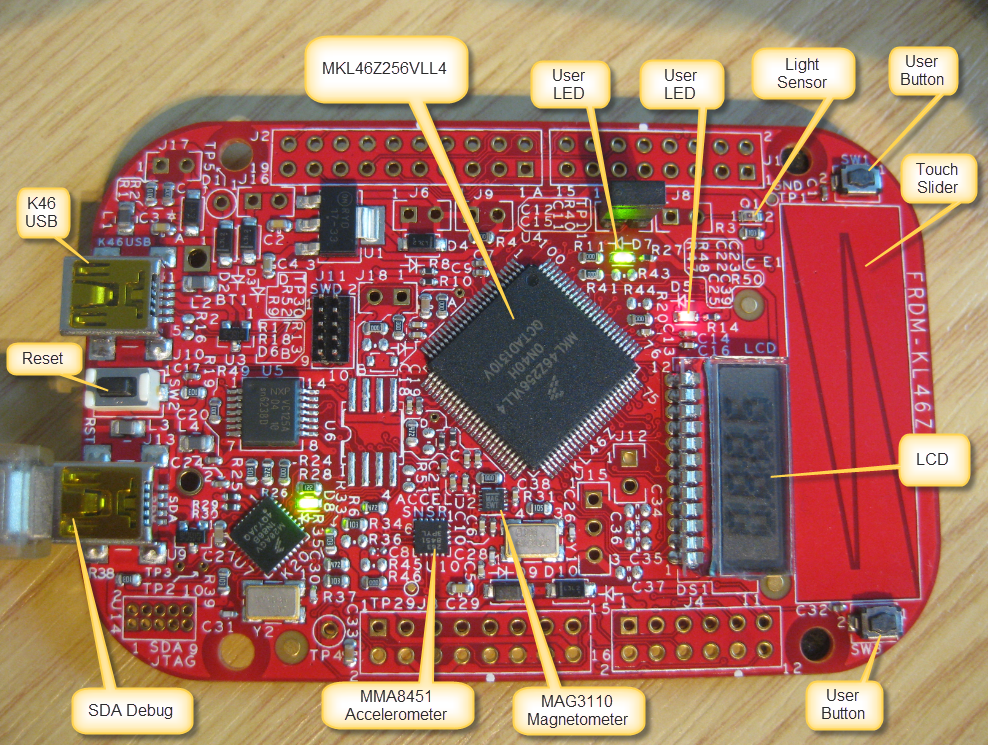

Hướng dẫn cài đặt phần mềm Keil uVision MDK-ARM và các packages cho bo mạch FRDM-KL46Z

Tải phần mềm Keil MDL-ARM từ địa chỉ: https://www2.keil.com/mdk5 và cài đặt theo hướng dẫn. Sau khi cài đặt xong MDK Core, trình cài đặt gói “Pack Installer” sẽ tự…