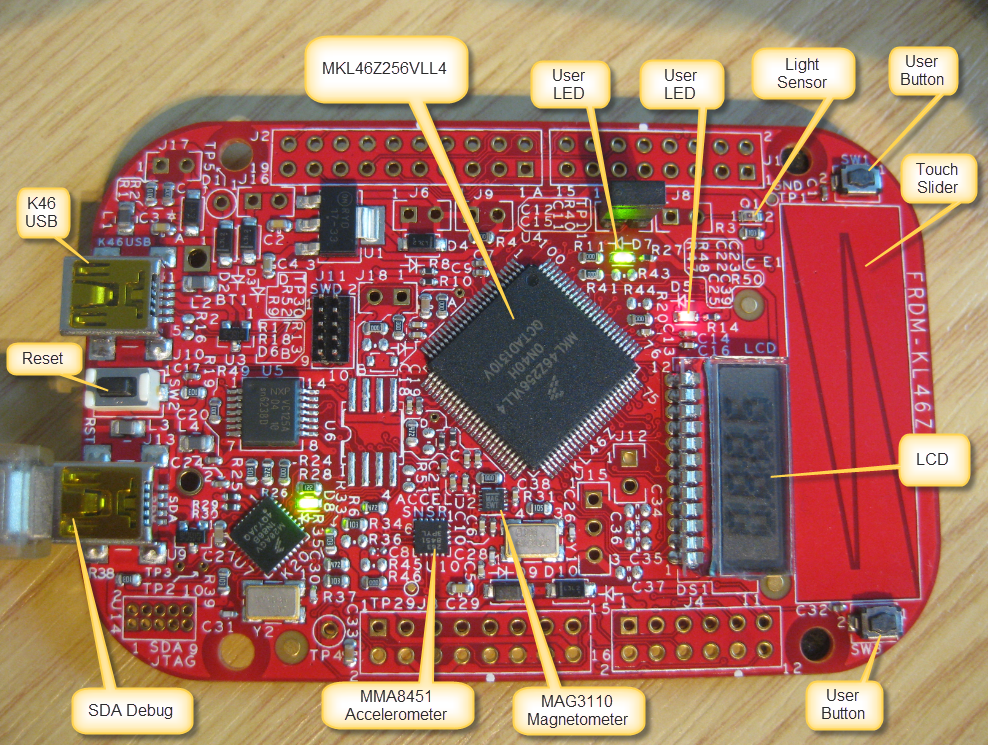

Do các bộ biến đổi tương tự – số ADC được sử dụng rộng rãi trong thu thập dữ liệu nên trong những năm gần đây ngày càng có nhiều bộ vi điều khiển tích hợp sẵn các mô-đun ADC trên chip. Trong phần này, chúng ta sẽ thảo luận về tính năng và cách lập trình mô-đun ADC của chip vi điều khiên Freescale KL46Z trên bo mạch FRDM-Kl46Z.

Bạn đọc có thể tìm mua bo mạch ở đây (Đang có chương trình khuyến mại giảm giá 15%).

Hình 6‑7. Sơ đồ khối mô-đun ADC0 trên chip Freescale KL46Z (hình 28-1, [14]).

Dòng chip Freescale KL46Z tích hợp sẵn một mô-đun ADC kiểu xấp xỉ liên tiếp có độ phân giải 16 bit được đặt tên là ADC0. Hình 6‑7 chỉ ra sơ đồ khối của mô-đun ADC trên chip Freescale KL46Z (chương 28 tài liệu tham khảo [14]). Mô-đun ADC hỗ trợ tới 4 cặp kênh đầu vào tương tự vi sai và 24 kênh đầu vào tương tự đơn cực. Mỗi cặp kênh vi sai yêu cầu hai đầu vào ký hiệu là DADPx và DADMx. Mô-đun cũng có 4 tín hiệu để cung cấp điện áp nguồn tương tự (VDDA), đất tương tự (VSSA) và điện áp tham chiếu mức cao (VREFSH) và mức thấp (VREFSL). ADC có thể được cấu hình để chấp nhận một trong hai cặp tham chiếu điện áp cho VREFSH và VREFSL. Hai cặp tham chiếu điện áp là (VREFH và VREFL) và (VALTH và VALTL). Các tham chiếu điện áp này được chọn bằng thanh ghi SC2[REFSEL] (chi tiết được mô tả bên dưới). Cặp tham chiếu điện áp VALTH và VALTL có thể được chọn lấy từ các chân bên ngoài hoặc từ nguồn bên trong tùy thuộc vào cấu hình MCU.

Để lập trình mô-đun ADC này chúng ta cần hiểu một số thanh ghi chính của nó. Hình 6‑8 cho thấy sơ đồ khối đã được đơn giản hóa của mô-đun ADC trên chip KL46Z với các thanh ghi chính dùng để giao tiếp với ADC đã được làm nổi bật.

Hình 6‑8. Sơ đồ khối đã được làm đơn giản của mô-đun ADC trên chip Freescale KL46Z.

Trong phần này, chúng ta tìm hiểu một số các thanh ghi này và chỉ ra cách lập trình ADC. Bảng 6‑4 dưới đây là một số thanh ghi chính của KL46Z ADC được tóm tắt từ tài liệu tham khảo KL46Z [14].

Bảng 6‑4. Các thanh ghi của mô-đun ADC trên chip KL46Z.

| Địa chỉ (tuyệt đối) | Tên thanh ghi | Khả năng truy xuất | Giá trị Reset |

| 4003 B000 | Thanh ghi điều khiển và trạng thái 1 (ADC0_SC1A) | R/W | 0000 001F |

| 4003 B004 | Thanh ghi điều khiển và trạng thái 1 (ADC0_SC1B) | R/W | 0000 001F |

| 4003 B008 | Thanh ghi cấu hình ADC 1 (ADC0_CFG1) | R/W | 0000 0000 |

| 4003 B00C | Thanh ghi cấu hình ADC 2 (ADC0_CFG2) | R/W | 0000 0000 |

| 4003 B010 | Thanh ghi kết quả biến đổi ADC (ADC0_RA) | R | 0000 0000 |

| 4003 B014 | Thanh ghi kết quả biến đổi ADC (ADC0_RB) | R | 0000 0000 |

| 4003 B018 | Thanh ghi giá trị so sánh (ADC0_CV1) | R/W | 0000 0000 |

| 4003 B01C | Thanh ghi giá trị so sánh (ADC0_CV2) | R/W | 0000 0000 |

| 4003 B020 | Thanh ghi điều khiển và trạng thái 2 (ADC0_SC2) | R/W | 0000 0000 |

| 4003 B024 | Thanh ghi điều khiển và trạng thái 3 (ADC0_SC3) | R/W | 0000 0000 |

Kích hoạt cấp xung nhịp cho ADC

Điều đầu tiên chúng ta cần làm là kích hoạt xung nhịp cho mô-đun ADC0. Bit D27 của thanh ghi SIM_SCGC6 được sử dụng để cho phép cấp xung nhịp tới mô-đun ADC0. SIM_SCGC6 là một phần của mô-đun tích hợp hệ thống SIM (chương 12 tài liệu tham khảo [14]) và được đặt tại địa chỉ vật lý 0x4004 7000 + 103C = 0x4000 803C. Xem Hình 6‑9.

Hình 6‑9. Thanh ghi SIM_SCGC6 chứa bit điều khiển cấp xung nhịp cho mô-đun ADC0.

Tùy chọn kích hoạt chuyển đổi

Có hai tùy chọn để kích hoạt bắt đầu quá trình chuyển đổi là kích hoạt bằng phần cứng và kích hoạt bằng phần mềm. Việc lựa chọn kích hoạt bằng phần cứng hoặc bằng phần mềm cho quá trình chuyển đổi được thực hiện thông qua bit D6 (ký hiệu là ADTRG – ADC Trigger) của thanh ghi ADC0_SC2 (ADC0 status control – thanh ghi điều khiển và trạng thái 2 của ADC0) (Hình 6‑10). Bộ kích hoạt phần cứng có thể lấy từ chân ngoài, bộ so sánh hoặc bộ hẹn giờ (TPMx, LPTMR0, PIT hoặc RTC). Việc lựa chọn bộ kích hoạt phần cứng được thực hiện bằng thanh ghi SIM_SOPT7. Bộ kích hoạt mặc định là phần mềm.

Hình 6‑10. Thanh ghi ADCx_SC2.

Bảng 6‑5 Mô tả chức năng các bit trong thanh ghi ADCx_SC2.

| Bit | Tên trường | Miêu tả |

| 7 | ADACT (ADC Conversion Active) | Cho biết ADC đang trong quá trình biến đổi hay không?

0: Quá trình biến đổi không diễn ra 1: Quá trình biến đổi đang diễn ra |

| 6 | ADTRG (ADC conversion trigger select) | Chọn lựa bộ kích hoạt quá trình biến đổi ADC

0: bộ kích hoạt phần mềm 1: bộ kích hoạt phần cứng |

| 5 | ACFE (ADC compare function enable) | Cho phép chức năng so sánh

0: chức năng so sánh bị cấm 1: chức năng so sánh được cho phép |

| 4 | ACFGT (ADC Compare Function Greater Than Enable) | Cho phép chức năng so sánh lớn hơn |

| 3 | ACREN (ADC Compare Range Enable) | Cho phép dải so sánh |

| 2 | DMAEN (DMA Enable) | Cho phép chức năng DMA |

| 1-0 | REFSEL (Voltage Reference Select) | Chọn lựa điện áp chiếu

00: Các chân VREFH và VREFL được sử dụng làm các điện áp tham chiếu VREF(+) và VREF(-) một cách tương ứng. 01: VALTH và VALTL được sử dụng làm cặp điện áp tham chiếu. Các tổ hợp khác: chưa được sử dụng |

Chọn kênh đầu vào Vin

Việc lựa chọn kênh tương tự đầu vào được thực hiện thông qua thanh ghi ADC0_SC1A (ADC0 Status and Control 1A – Thanh ghi trạng thái và điều khiển 1A của ADC0). Lưu ý rằng có nhiều thanh ghi ADC0_SC1n nhưng chỉ có thể sử dụng thanh ghi ADC0_SC1A để kích hoạt quá trình chuyển đổi của ADC0 bằng phần mềm. Các thanh ghi khác chỉ dành cho kích hoạt bằng phần cứng và sẽ không được thảo luận ở đây. Năm bit thấp nhất của thanh ghi ADC0_SC1A được sử dụng để chọn một trong 31 kênh đầu vào tương tự sẽ được chuyển đổi. Xem Hình 6‑11.

Hình 6‑11. Thanh ghi ADCx_SC1A.

Bảng 6‑6. Mô tả chức năng các bit trong thanh ghi ADCx_SC1A.

| Bit | Tên trường | Miêu tả |

| 7 | COCO (Conversion Complete | Cờ báo quá trình chuyển đổi hoàn thành

0: Quá trình chuyển đổi đã hoàn thành 1: Quá trình chuyển đổi chưa hoàn thành |

| 6 | AIEN (Interrupt Enable) | Cho phép ngắt từ ADC. Ngăt từ ADC được cho phép bằng cách thiết lập bit lên mức cao. Nếu cho phép ngắt được thiết lập thì một ngắt sẽ được tạo ra khi cờ COCO được đặt. |

| 5 | DIFF (Differential Mode) | Chọn chế độ vi sai

0: chế độ đơn cực 1: chế độ vi sai |

| 4-0 | ADCH (ADC input Channel) | Chọn kênh đầu vào tương tự như chỉ ra trong Hình 6‑8.

Khi DIFF = 0 (chế độ đơn cực), giá trị 0 – 23 trên ADCH chọn một trong 24 kênh đầu vào (ADC_SE0 đến ADC_SE23). Khi DIFF = 1 (chế độ vi sai), giá trị 0 – 3 trên ADCH chọn một trong 4 kênh vi sai đầu vào (Tham khảo [14] để bieert thêm chi tiết). Khi ADCH = 11111, mô-đun bị cấm |

Bảng 6‑7 chỉ ra quy định về cách gán kênh tới các chân của vi điều khiển KL46Z. Chi tiết về việc chọn kênh đầu vào và gán kênh tới các chân điều khiển tham khảo phần 3.7.1.3.1 và 10.3.1 và của tài liệu hướng dẫn sử dụng KL46Z [14]. Lưu ý là không phải tất cả các kênh đều được kết nối với các chân đầu vào của chip vi điều khiển và số lượng kênh có sẵn là khác nhau giữa các thành viên trong dòng Freescale KL46Z.

Bảng 6‑7. Gán kênh ADC tới các chân của vi điều khiển Freescale Kl46Z.

| SC1[ADCH]

(bit) |

Kênh ADC | SC1[DIFF] = 1 | SC1[DIFF] = 0 | Chân |

| 00000 | DAD0 | ADC0_DP0 và ADC0_DM0 | ADC0_DP0/ADC0_SE0 | PTE20 |

| 00001 | DAD1 | ADC0_DP1 và ADC0_DM1 | ADC0_DP1/ADC0_SE1 | PTE16 |

| 00010 | DAD2 | ADC0_DP2 và ADC0_DM2 | ADC0_DP2/ADC0_SE2 | PTE18 |

| 00011 | DAD3 | ADC0_DP3 và ADC0_DM3 | ADC0_DP3/ADC0_SE3 | PTE22 |

| 001001 | AD4a | Không sử dụng | ADC0_DM0/ADC0_SE4a | PTE21 |

| 001011 | AD5a | Không sử dụng | ADC0_DM1/ADC0_SE5a | PTE17 |

| 001101 | AD6a | Không sử dụng | ADC0_DM2/ADC0_SE6a | PTE19 |

| 001111 | AD7a | Không sử dụng | ADC0_DM3/ADC0_SE7a | PTE23 |

| 001001 | AD4b | Không sử dụng | ADC0_SE4b | PTE29 |

| 001011 | AD5b | Không sử dụng | ADC0_SE5b | PTD1 |

| 001101 | AD6b | Không sử dụng | ADC0_SE6b | PTD5 |

| 001111 | AD7b | Không sử dụng | ADC0_SE7b | PTD6 |

| 01000 | AD8 | Không sử dụng | ADC0_SE8 | PTB0 |

| 01001 | AD9 | Không sử dụng | ADC0_SE9 | PTB1 |

| 01011 | AD11 | Không sử dụng | ADC0_SE11 | PTC2 |

| 01100 | AD12 | Không sử dụng | ADC0_SE12 | PTB2 |

| 01101 | AD13 | Không sử dụng | ADC0_SE13 | PTB3 |

| 01110 | AD14 | Không sử dụng | ADC0_SE14 | PTC0 |

| 01111 | AD15 | Không sử dụng | ADC0_SE15 | PTC1 |

| 10111 | AD23 | Không sử dụng | 12-bit DAC0 Output/ADC0_SE23 | PTE30 |

| 11010 | AD26 | Temperature Sensor (Diff) | Temperature Sensor (S.E) | |

| 11011 | AD27 | Bandgap (Diff) | Bandgap (S.E) | |

| 11101 | AD29 | -VREFH (Diff) | VREFH (S.E) | |

| 11110 | AD30 | Không sử dụng | VREFL | |

| 11111 | AD31 | Mô-đun bị cấm | Mô-đun bị cấm |

Cơ chế thăm dò và ngắt trong giám sát trạng thái ADC

Kết thúc quá trình chuyển đổi được chỉ thị bằng một bit cờ trong thanh ghi điều khiển và trạng thái ADC0_SC1A. Sau khi hoàn thành chuyển đổi, cờ hoàn thành chuyển đổi (COCO) tương ứng với bit D7 sẽ được đặt lên mức cao. Bằng cách thăm dò cờ này, chúng ta biết được quá trình chuyển đổi đã hoàn tất và chúng ta có thể đọc giá trị trong thanh ghi kết quả dữ liệu ADC0_RA. Chúng ta cũng có thể sử dụng cơ chế ngắt để thông báo rằng quá trình chuyển đổi đã hoàn tất nhưng điều đó sẽ yêu cầu chúng ta phải đặt bit cho phép ngắt AIEN (bit 6) trong thanh ghi ADC0_SC1A lên mức cao. Theo mặc định, ngắt không được kích hoạt.

Kết quả chuyển đổi ADC

Sau khi hoàn thành chuyển đổi, kết quả số được đặt trong thanh ghi ADC0_RA. Lưu ý là có nhiều thanh ghi ADC0_Rn tương ứng với các thanh ghi ADC0_SC1n. Bởi vì chúng ta chỉ có thể sử dụng ADC0_SC1A để kích hoạt quá trình ADC bằng phần mềm, dữ liệu sẽ trả về trong thanh ghi ADC0_RA tương ứng. Đây là thanh ghi 32 bit nhưng chỉ 16 bit thấp hơn được sử dụng như chỉ ra trong Hình 6‑12. Chúng ta có các tùy chọn độ phân giải 8-, 10-, 12- và 16-bit cho kết quả chuyển đổi ADC không dấu đơn cực. Trong mọi trường hợp, kết quả luôn luôn được căn chỉnh phải và các bit còn lại cho đến bit D15 không được sử dụng. Nếu kết quả được mã hóa bù 2 cho biến đổi ADC kênh vi phân, thì cơ chế mở rộng dấu được thực hiện trên các bit còn lại đến bit D15. Chi tiết tham khảo bảng 28-43 của tài liệu tham khảo [14].

Hình 6‑12. Thanh ghi kết quả chuyển đổi ADC.

Xóa cờ báo hoàn thành chuyển đồi

Bit cờ báo hoàn thành chuyển đổi COCO trong thanh ghi ADCx_SC1n được xóa tự động khi dữ liệu từ thanh ghi ADCx_Rn được đọc.

Kênh vi sai so với kênh đơn cực

Trong một số ứng dụng, mối quan tâm của chúng ta là sự khác biệt giữa hai điện áp tín hiệu tương tự (hay còn gọi là điện áp vi sai). Thay vì chuyển đổi hai kênh tách biệt và tính toán sự khác biệt giữa chúng, KL46Z có tùy chọn cho việc chuyển đổi điện áp vi sai của hai kênh tương tự. Bit D5 (có tên là DIFF) của thanh ghi ADC0_SC1A cho phép chúng ta kích hoạt tùy chọn kênh vi sai. Khi reset hệ thống, chế độ hoạt động mặc định của ADC là đầu vào đơn cực. Xem tài liệu tham khảo hướng dẫn sử dụng KL46Z [14] để biết thêm thông tin về các tùy chọn vi sai.

Lựa chọn độ phân giải

Chúng ta sử dụng thanh ghi cấu hình ADC0_CFG1 (Hình 6‑13) để thiết lập số bit phân giải cho ADC là 8, 10, 12 hay 16 bit. Thanh ghi này cũng được sử dụng để chọn lựa tốc độ của nguồn xung nhịp cho ADC.

Hình 6‑13. Thanh ghi ADCx_CFG1.

Bảng 6‑8. Mô tả chức năng các trường trong thanh ghi ADCx_CFG1.

| Bit | Tên trường | Miêu tả | |||||||||||||||

| 7 | ADLPC (Low-Power Configuration) | Cấu hình chế độ hoạt động tiết kiệm năng lượng | |||||||||||||||

| 6-5 | ADIV (ADC Clock Divide) | Lựa chọn hệ số chia cho tín hiệu clock. Tín hiệu clock nguồn sẽ được chia cho 2ADIV như được chỉ ra trong Hình 6‑8. | |||||||||||||||

| 4 | ADLSMP | Cấu hình thời gian lấy mẫu

0: thời gian lấy mẫu ngắn 1: thời gian lấy mẫu dài |

|||||||||||||||

| 3-2 | MODE | Lựa chọn chế độ chuyển đổi

|

|||||||||||||||

| 1-0 | ADICLK | Chọn lựa nguồn clock đầu vào:

|

Lưu ý trong thanh ghi ADCx_CFG1, các bit MODE (D3: D2) chọn độ phân giải. Cũng lưu ý, nếu chúng ta sử dụng tùy chọn chế độ hoạt động công suất thấp với bit D7, thì tốc độ chuyển đổi bị giới hạn.

Thời gian chuyển đổi ADC

Thời gian chuyển đổi cho ADC chia làm ba pha như sau:

1) Trong pha đầu tiên, một bộ khuếch đại mẫu với hệ số khuếch đại đơn vị (tương ứng một bộ đệm) lấy mẫu đầu vào tương tự trong tổng số n chu kỳ xung nhịp. Bộ đệm sạc tụ điện lấy mẫu tới điện áp đầu vào.

2) Trong pha thứ hai, bộ đệm mẫu bị ngắt kết nối và được kết nối với nút lưu trữ trong một số chu kỳ xung nhịp nhất định. Số chu kỳ xung nhịp có thể là 4, 6, 10, 16 hoặc 24. Chúng ta có thể lập trình số chu kỳ này thông qua bit ADLSMP trong thanh ghi ADCx_CFG1 và các bit ADLSTS trong thanh ghi ADCx_CFG2 (Hình 6‑14). Thời gian lấy mẫu lâu hơn đảm bảo rằng điện áp của tụ điện mẫu được đưa đến gần hơn với điện áp đầu vào. Điều này rất quan trọng khi điện áp đầu vào khác nhau đáng kể từ mẫu này sang mẫu khác. Nhưng nó cũng làm kéo dài thời gian chuyển đổi của từng mẫu.

3) Trong pha thứ ba, đầu vào tương tự được chuyển đổi thành số nhị phân bằng phương pháp xấp xỉ liên tiếp. Trong pha này, số lượng xung nhịp được sử dụng phụ thuộc vào số lượng bit trong đầu ra nhị phân. Đối với mỗi bit chúng ta cần một xung nhịp. Điều đó có nghĩa là chúng ta cần 8 xung nhipk cho đầu ra 8 bit, 10 xung nhịp cho đầu ra 10 bit, v.v. Chúng ta chọn tùy chọn độ phân giải n-bit bằng cách sử dụng các bit MODE của thanh ghi ADCx_CFG1.

Thanh ghi ADCx_CFG1 cung cấp cho chúng ta nhiều cách tùy chọn xung nhịp được cung cấp cho mô-đun ADC. Chúng ta có thể chọn xung nhịp Bus hoặc một phần của nó. Sử dụng các bit ADICLK (ADC input Clock: xung nhịp đầu vào ADC) và ADIV (ADC Divide: hệ số chia) của thanh ghi ADCx_CFG1, chúng ta có thể kiểm soát tốc độ của nguồn xung nhịp được cung cấp cho ADC. Kết hợ các bit này cùng với các bit trong thanh ghi ADCx_CFG2, chúng ta có thể kiểm soát thời gian chuyển đổi.

Hình 6‑14. Thanh ghi ADCx_CFG2.

Vref trên bo mạch FRDM-KL46Z

Trong chip ARM KL46Z của Freescale, chân cho Vref (+) được gọi là VREFH (Vref High) và chân Vref (-) được gọi là VREFL (Vref Low). Trên bo mạch FRDM-KL46Z, chân VREFH được kết nối tới cùng nguồn điện áp cung cấp với phần mạch số của chip là 3,3V. Mạch có thể được thay đổi để sử dụng chân AREF cho điện áp tham chiếu bên ngoài. Ngay cả khi chúng ta kết nối VREFH với một tham chiếu bên ngoài khác với VDD của chip, nó không thể vượt quá điện áp VDD. Với VREFH = 3,3V, chúng ta có kích thước bước biến đổi là 3,3V/65,536 = 0,05 mV do độ phân giải ADC tối đa cho KL46Z là 16 bit.

| Ví dụ 6‑2 |

| Trên bo mạch FRDM- KL46Z nếu điện áp tương tự đầu vào là 1,2V hãy tính giá trị số đầu ra. |

| Đáp án:

Vì kích thước bước là 3,3V/65536 = 0,05mV, chúng ta có giá trị số đầu ra là 1,2V/0,05mV = 23.831 = 0x5D17 |

Quy trình cấu hình và đọc kênh ADC

Khi sử dụng ADC, chúng ta cũng phải cấu hình các chân GPIO để cho phép kết nối tín hiệu tương tự thông qua chân đầu vào. Chúng ta cần thực hiện các bước sau để cấu hình ADC:

- Cho phép cấp xung nhịp tới chân I/O được sử dụng bởi kênh ADC. Tham khảo Bảng 7-7 để biết các chân I/O được sử dụng bởi các kênh ADC như thế nào.

- Đặt bit các bit MUX trong thanh ghi PORTX_PCRn tương ứng với chân được dùng làm đầu vào ADC thành 0 để sử dụng chân làm kênh đầu vào tương tự. Lưu ý, đây chính là cấu hình mặc định khi bật nguồn của thanh ghi PORTX_PCRn.

- Cho phép cấp xung nhịp cho mô-đun ADC0 bằng thanh ghi SIM_SCGC6.

- Thiết lập bộ kích hoạt phần mềm bằng thanh ghi ADC0_SC2.

- Thiết lập tốc độ xung nhịp và độ phân giải bằng thanh ghi ADC0_CFG1.

- Thiết lập kênh đầu vào ADC bằng thanh ghi ADC0_SC1A. Sử dụng Bảng 7-7 để chọn chân và kênh phù hợp. Đảm bảo ngắt không được kích hoạt và tùy chọn kết thúc đơn được sử dụng khi bạn chọn kênh với thanh ghi này.

- Tiếp tục theo dõi cờ báo kết thúc chuyển đổi COCO trong thanh ghi ADC0_SC1A.

- Khi cờ COCO chuyển lên mức CAO, hãy đọc kết quả ADC từ ADC0_RA và lưu nó.

- Lặp lại các bước 6 đến 8 cho lần chuyển đổi tiếp theo.

Chương trình 7‑1 minh họa các bước chuyển đổi ADC được nêu ở trên. Hình 6‑15 cho thấy kết nối phần cứng của Chương trình 7‑1.

/* p6_1.c: A to D conversion of channel 0

* This program converts the analog input from channel 0 (PTE20)

* using software trigger continuously.

* Bits 10-8 are used to control the tri-color LEDs. LED code is copied from p2_7.

* Connect a potentiometer between 3.3V and

* ground. The wiper of the potentiometer is connected to PTE20.

* When the potentiometer is turned, the LEDs should change color.

*/

#include “MKL46Z4.h”

void ADC0_init(void);

void LED_set(int s);

void LED_init(void);

int main (void)

{

short int result;

LED_init(); /* Configure LEDs */

ADC0_init(); /* Configure ADC0 */

while (1) {

ADC0->SC1[0] = 0; /* start conversion on channel 0 */

while(!(ADC0->SC1[0] & 0x80)) { } /* wait for conversion complete */

result = ADC0->R[0]; /* read conversion result and clear COCO flag */

LED_set(result >> 7); /* display result on LED */

}

}

void ADC0_init(void)

{

SIM->SCGC5 |= 0x2000; /* clock to PORTE */

PORTE->PCR[20] = 0; /* PTE20 analog input */

SIM->SCGC6 |= 0x8000000; /* clock to ADC0 */

ADC0->SC2 &= ~0x40; /* software trigger */

/* clock div by 4, long sample time, single ended 12 bit, bus clock */

ADC0->CFG1 = 0x40 | 0x10 | 0x04 | 0x00;

}

void LED_init(void) {

SIM->SCGC5 |= 0x400; /* enable clock to Port B */

SIM->SCGC5 |= 0x1000; /* enable clock to Port D */

PORTB->PCR[18] = 0x100; /* make PTB18 pin as GPIO */

PTB->PDDR |= 0x40000; /* make PTB18 as output pin */

PORTB->PCR[19] = 0x100; /* make PTB19 pin as GPIO */

PTB->PDDR |= 0x80000; /* make PTB19 as output pin */

PORTD->PCR[1] = 0x100; /* make PTD1 pin as GPIO */

PTD->PDDR |= 0x02; /* make PTD1 as output pin */

}

void LED_set(int s) {

if (s & 1) /* use bit 0 of s to control red LED */

PTB->PCOR = 0x40000; /* turn on red LED */

else

PTB->PSOR = 0x40000; /* turn off red LED */

if (s & 2) /* use bit 1 of s to control green LED */

PTB->PCOR = 0x80000; /* turn on green LED */

else

PTB->PSOR = 0x80000; /* turn off green LED */

if (s & 4) /* use bit 2 of s to control blue LED */

PTD->PCOR = 0x02; /* turn on blue LED */

else

PTD->PSOR = 0x02; /* turn off blue LED */

}

Hình 6‑15. Sơ đồ mạch phần cứng cho Chương trình 6‑1.

Cảm biến nhiệt độ

Có một số kênh tương tự nội bộ được tích hợp kèm ADC0 như được chỉ ra trong Bảng 6‑7. Chương trình tiếp theo chỉ ra cách để chuyển đổi đầu ra tương tự của cảm biến nhiệt độ bên trong vi điều khiển thành tín hiệu số. Để ý là trong phần khởi tạo ADC, chúng ta không cần khởi tạo chân đầu vào vì kênh được kết nối bên trong vi điều khiển.

Chương trình 6‑2: Chuyển đổi tín hiệu từ cảm biến nhiệt độ bên trong chip Kl46Z

/* p6_2.c: A to D conversion of internal temperature sensor

* This program converts the analog input from channel 26

* (internal temperature sensor) using software trigger continuously.

* Bits 2-0 are used to control the tri-color LEDs. LED code is

* copied from p2_7. Put your finger on the target MCU and watch

* LEDs change color.

*/

#include “MKL46Z4.h”

void ADC0_init(void);

void LED_set(int s);

void LED_init(void);

int main (void)

{

short int result;

LED_init(); /* Configure LEDs */

ADC0_init(); /* Configure ADC0 */

while (1) {

ADC0->SC1[0] = 26; /* start conversion on channel 26 temperature */

while(!(ADC0->SC1[0] & 0x80)) { } /* wait for COCO */

result = ADC0->R[0]; /* read conversion result and clear COCO flag */

LED_set(result); /* display result on LED */

}

}

void ADC0_init(void)

{

SIM->SCGC6 |= 0x8000000; /* clock to ADC0 */

ADC0->SC2 &= ~0x40; /* software trigger */

/* clock div by 4, long sample time, single ended 12 bit, bus clock */

ADC0->CFG1 = 0x40 | 0x10 | 0x04 | 0x00;

}

void LED_init(void) {

SIM->SCGC5 |= 0x400; /* enable clock to Port B */

SIM->SCGC5 |= 0x1000; /* enable clock to Port D */

PORTB->PCR[18] = 0x100; /* make PTB18 pin as GPIO */

PTB->PDDR |= 0x40000; /* make PTB18 as output pin */

PORTB->PCR[19] = 0x100; /* make PTB19 pin as GPIO */

PTB->PDDR |= 0x80000; /* make PTB19 as output pin */

PORTD->PCR[1] = 0x100; /* make PTD1 pin as GPIO */

PTD->PDDR |= 0x02; /* make PTD1 as output pin */

}

void LED_set(int s) {

if (s & 1) /* use bit 0 of s to control red LED */

PTB->PCOR = 0x40000; /* turn on red LED */

else

PTB->PSOR = 0x40000; /* turn off red LED */

if (s & 2) /* use bit 1 of s to control green LED */

PTB->PCOR = 0x80000; /* turn on green LED */

else

PTB->PSOR = 0x80000; /* turn off green LED */

if (s & 4) /* use bit 2 of s to control blue LED */

PTD->PCOR = 0x02; /* turn on blue LED */

else

PTD->PSOR = 0x02; /* turn off blue LED */

}