Bài viết trình bày thiết kế và mã nguồn VHDL thực hiện bộ giải mã từ mã nhị phân sang mã LED 7-đoạn.

Sơ đồ của mô-đun hiển thị LED bảy đoạn được hiển thị trong Hình 2‑1(a). Nó bao gồm bảy thanh LED và một LED đơn cho dấu thập phân. Giả thiết mô-đun hiển thị LED bảy đoạn trong ví dụ này hoạt động ở mức logic thấp, có nghĩa là một đoạn LED sẽ sáng nếu tín hiệu điều khiển tương ứng là 0.

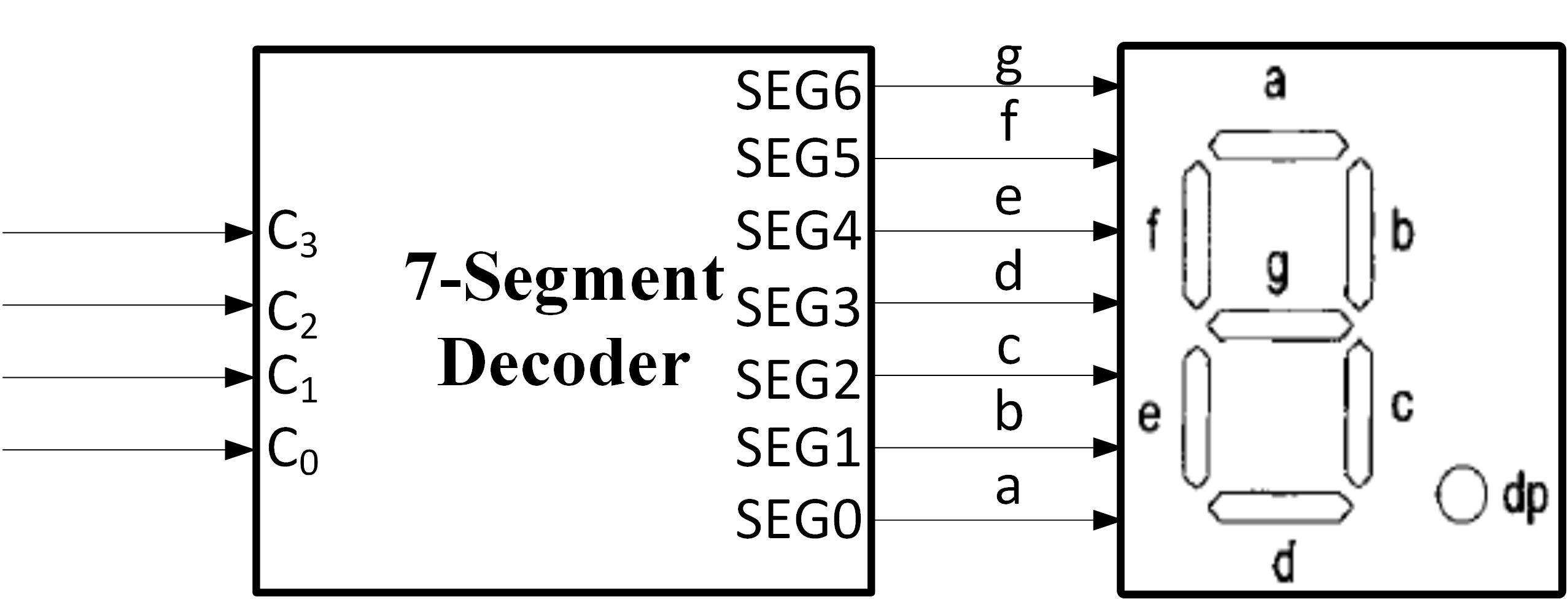

Hình 2‑2 chỉ ra sơ đồ ghép nối mô-đun hiển thị LED 7 với bộ giải mã từ mã nhị phân sang mã 7-đoạn. Đèn LED dấu thập phân không được kết nối và do đó không được sử dụng.

Bộ giải nhị phân sang mã 7 đoạn nhận đầu vào là 4 bit nhị phân dưới dạng chữ số thập lục phân và tạo ra các mẫu LED thích hợp như chỉ trong Hình 2‑1(b). Các tín hiệu điều khiển LED, a, b, c, d, e, f, g được nhóm lại với nhau dưới dạng tín hiệu 7 bit ký hiệu là SE(0 to 6).

Mã nguồn VHDL mô tả bộ giải mã từ mã nhị phân sang LED 7 đoạn được đưa ra trong Bảng 2‑1.

(a) Sơ đồ các thanh LED trên hiển thị LED 7 đoạn |

Hình 2‑1. Hiển thị LED 7-đoạn và các mẫu hiển thị các số thập lục phân

Hình 2‑2. Bộ giải mã LED 7 đoạn.

Bảng 2‑1. Mã nguồn VHDL thực hiện bộ giải mã từ mã nhị phân sang mã 7 đoạn

| 1

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 |

———————————————————————————-

— Company: VNU-UET — Engineer: Nguyen Kiem Hung — — Create Date: 05/13/2017 03:50:57 PM — Design Name: Binary to 7-segment Decoder ———————————————————————————- library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; — Uncomment the following library declaration if using — arithmetic functions with Signed or Unsigned values –use IEEE.NUMERIC_STD.ALL; entity Bin2SEG is Port ( C : in STD_LOGIC_VECTOR (3 downto 0); SEG : out STD_LOGIC_VECTOR (0 to 6) ); end Bin2SEG; architecture BEV of Bin2SEG is –signal SEG : STD_LOGIC_VECTOR(DATA_WIDTH – 1 downto 0); begin process(C) begin case C is when “0000” => — 0 SEG <= “0000001”; when “0001” => — 1 SEG <= “1001111”; when “0010” => — 2 SEG <= “0010010”; when “0011” => — 3 SEG <= “0000110”; when “0100” => — 4 SEG <= “1001100”; when “0101” => –5 SEG <= “0100100”; when “0110” => — 6 SEG <= “0100000”; when “0111” => — 7 SEG <= “0001111”; when “1000” => — 8 SEG <= “0000000”; when “1001” => — 9 SEG <= “0000100”; when “1010” => — A SEG <= “0001000”; when “1011” => — b SEG <= “1100000”; when “1100” => — c SEG <= “0110001”; when “1101” => — d SEG <= “1000010”; when “1110” => — e SEG <= “0110000”; when “1111” => — f SEG <= “0111000”; when others => — Preset SEG <= (others => ‘1’); end case; end process; end BEV; |

Bảng 2‑2. Mã nguồn testbench cho bộ giải mã

| 1

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |

LIBRARY ieee;

USE ieee.std_logic_1164.all; use IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY Bin2SEG_tb IS END Bin2SEG_tb; ARCHITECTURE Bin2SEG_tb_architecture OF Bin2SEG_tb IS — Component declaration of the tested unit COMPONENT Bin2SEG Port ( C : in STD_LOGIC_VECTOR (3 downto 0); SEG : out STD_LOGIC_VECTOR (0 to 6) ); END COMPONENT; — Stimulus signals – signals mapped to the input and inout ports of tested entity SIGNAL C: STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL SEG : STD_LOGIC_VECTOR (0 to 6); BEGIN UUT : Bin2SEG PORT MAP ( C => C, SEG => SEG); Testing: PROCESS BEGIN C<= “0000”; FOR i IN 0 TO 15 LOOP WAIT FOR 10 ns; c <= c+”0001″; END LOOP; END PROCESS; END Bin2SEG_tb_architecture; |