IC (Integrated Circuit) Design flow

Hình 1. Quy trình thiết kế IC.

Hình 1 chỉ ra các công đoạn khác nhau trong quy trình từ thiết kế, kiểm chứng đến chế tạo vi mạch ASIC (Application-specific Integrated Circuit) và chạy thử nghiệm. Về tổng thể luồng thiết kế được chia thành 4 công đoạn, gồm: thiết kế cấu trúc, tổng hợp lô-gic thiết kế, thực hiện thiết kế ở mức vật lý, sản xuất và kiểm thực vi mạch. Luồng thiết kế bắt đầu bằng việc xây dựng một bản đặc tả các yêu cầu mà thiết kế cần phải thỏa mãn. Bản đặc tả này chỉ ra mục tiêu, tính năng và các ràng buộc (constraints) như hiệu năng (tốc độ xử lý), công suất tiêu thụ, kích thước vật lý, kỹ thuật thiết kế, công nghệ chế tạo, …mà thiết kế thiết kế phải thỏa mãn.

Từ bản đặc tả người thiết kế đề xuất cấu trúc của thiết kế và thực hiện mô hình hóa cấu trúc đó ở mức truyền thanh ghi RTL (Register Transfer Level) bằng một ngôn ngữ mô tả phần cứng như Verilog hoặc VHDL. Để thuận tiện cho quá trình thiết kế và kiểm tra, một thiết kế lớn thường được chia thành một vài mô đun con. Mỗi mô đun này thực hiện một chức năng xác định trong hệ thống tổng thể và có những ràng buộc riêng để đảm bảo rằng khi chúng được tích hợp lại với nhau thì cả hệ thống sẽ thỏa mãn các ràng buộc trong bản đặc tả. Kiểm chứng chức năng mức RTL được thực hiện ở bước này để đảm bảo mô hình RTL được thiết kế đúng như các yêu cầu trong đặc tả.

Bước tiếp theo là tổng hợp Lô-gic/RTL, trong đó mô hình RTL sẽ được chuyển đổi thành một bản mô tả cấu trúc của thiết kế ở mức cổng lô-gic (Gate Level Netlist) bởi một số các công cụ tổng hợp như Design Compiler (Synopsys), Blast Create (Magma), RTL Compiler (Cadence), … Công cụ tổng hợp sử dụng bản miêu tả RTL và thư viện các khối xây dựng cơ bản cho thiết kế IC (Standard Cell library) như lối vào để tạo ra netlist ở lối ra. Các ràng buộc như thời gian (timing), diện tích (area), công suất tiêu thụ, và hỗ trợ khả năng kiểm tra (Design for Test) cần được đánh giá trong bước này. Công cụ tổng hợp cố gắng tìm ra một phương án thực thi tốt nhất thỏa mãn các ràng buộc và quy trình công nghệ đã được xác định. Ở giai đoạn này, thiết kế cũng cần được kiểm tra để đảm bảo rằng quá trình chuyển đổi từ mức RTL sang mức cổng lô-gic không đưa vào bất kỳ lỗi gì.

Trong pha thực hiện thiết kế ở mức vật lý tiếp theo, biểu diễn lô-gic của thiết kế trong Netlist sẽ được chuyển đổi thành dạng biểu diễn hình học, tức là thực hiện sắp xếp các khối xây dựng của thiết kế trong một không gian vật lý xác định. Quá trình này vì thế cũng thường được gọi là quá trình Layout thiết kế. Quá trình Layout cần tuân thủ các quy tắc thiết kế được xác định trong thư viện công nghệ được sử dụng. Pha thực hiện thiết kế ở mức vật lý bao gồm 3 bước nhỏ: Floor planning (quy hoạch), Placement (Đặt linh kiện) và Routing (Đi dây). Dữ liệu được tạo ra ở lối ra của quá trình thực hiện vật lý, được gọi là tệp dữ liệu GDSII, sẽ được gửi tới các nhà máy chế tạo IC. Tại nhà máy chế tạo, dữ liệu layout được dùng để tạo ra các mặt nạ chế tạo ra vi mạch ASIC. Sau khi chế tạo, wafer được chia thành các miếng nhỏ riêng lẻ gọi là chip. Mỗi Chip được đóng gói thành các linh kiện như chúng ta thường thấy trong Hình 2. Quá trinh layout này có thể được thực hiện bởi một trong các công cụ như: Blast Fusion (Magma), IC Compiler (Synopsys), và Encouter (Cadence), … Kiểm tra vật lý được thực hiện để đảm bảo layout được thiết kế đúng quy tắc, cũng như thỏa mãn tất cả các ràng buộc trong bản đặc tả.

Hình 2. Các bước trong chế tạo IC.

Trong quá trình thiêt kế, phân tích hoạt động của thiết kế theo thời gian (timing analysis) được thực hiện nhằm đảm bảo thiết kế làm việc ở một tốc độ yêu cầu như được đề cập trong đặc tả. Bước này thường được thực hiện bởi công cụ phân tích thời gian tĩnh (Static timing Analysis Tool) chẳng hạn như Primetime (Synopsys). Công cụ này giúp kiểm thực hiệu năng được định thời của thiết kế bằng việc thử nghiệm thiết kế với tất cả các vi phạm thời gian như setup, hold timing.

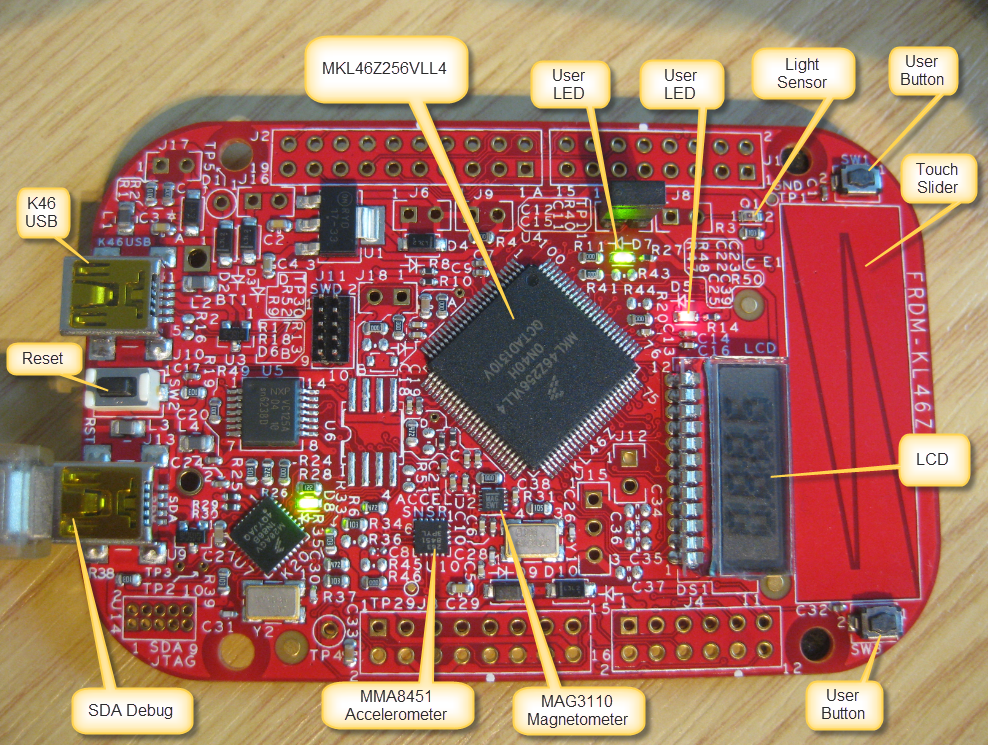

Cuối cùng sau khi nhận được vi mạch mẫu từ nhà máy chế tạo, vi mạch cần được kiểm chứng với một vài ứng dụng khác nhau trên một bo mạch demo thực tế. Mục đích của việc kiểm chứng này là để chứng minh tính đúng đắn của hệ thống đã được thiết kế chế tạo theo các thông số kỹ thuật đề ra trong bản đặc tả.