NỘI DUNG

RTL Design and VHDL code for the DMAC with a built-in Sorting Unit

VHDL CODE CAN BE DOWNLOAD HERE.

1. Mục tiêu

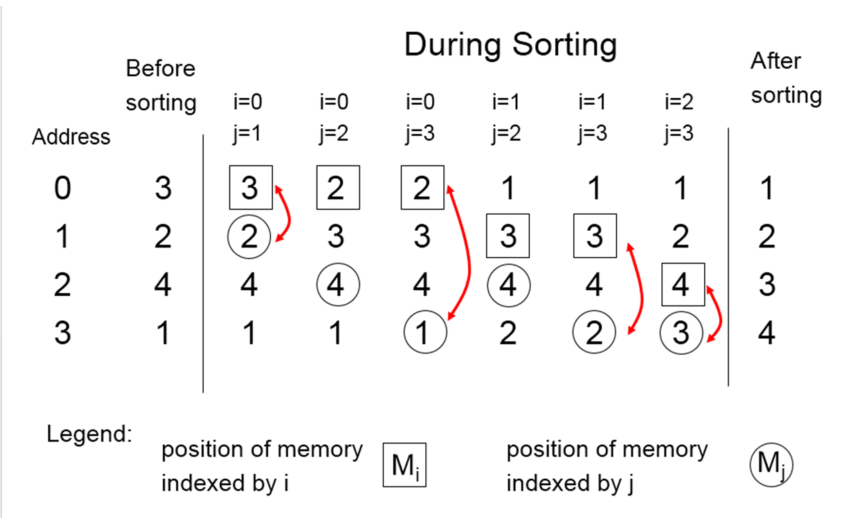

Thiết kế mức RTL, mô hình hóa bằng VHDL, mô phỏng bằng ModelSIM và thực thi một bộ truy xuất bộ nhớ trực tiếp DMAC tích hợp đơn vị sắp xếp (Sorting Unit) một dãy số theo trật tự tăng hoặc giảm dần. Chức năng sắp xếp một dãy số theo trậ tự tăng dần được minh họa như được chỉ ra trong hình dưới.

Hình 1. Ví dụ minh họa quá trình sắp xếp một dãy gồm 4 phần tử theo trật tự tăng dần.

2. Yêu cầu đối với thiết kế:

- Giao diện vào ra tương thích với kiến trúc mảng tái cấu hình cấu trúc thô MUSRA

- Kích thước dãy số k, và độ rộng N-bit của mỗi phần tử của dãy số được khai báo như tham số cấu hình của thiết kế

- Sorting Unit có giao diện ghép nối với hệ thống vi xử lý như chỉ ra trong Hình 2 sao cho:

- Đơn vị xử lý trung tâm (CPU) có thể viết k phần tử của dãy số cần phân loại

tới bộ đệm bên trong của Sorting Unit. - Sau khi khởi tạo xong Sorting Unit, CPU sẽ kích hoạt quá trình tính toán của Sorting Unit bằng cách đặt tín hiệu Start = ‘1’

- Sau khi Sorting Unit kết thúc quá trình sắp xếp nó báo cho CPU biết bằng cách đặt tín hiệu Done = ‘1’; Sorting Unit cần giữ trạng thái này cho đến khi Start = 0.

- Khi Done = ‘1’, CPU có thể tiến hành đọc mảng dữ liệu đã được sắp xếp từ Sorting Unit

- Sau khi kết thúc đọc dữ liệu từ Sorting Unit, CPU xóa tín hiệu Start = 0 để báo phiên làm việc của Sorting Unit đã kết thúc.

- Đơn vị xử lý trung tâm (CPU) có thể viết k phần tử của dãy số cần phân loại

Hình 2. Giao diện ghép nối I/O của đơn vị Sorting Unit.

Định nghĩa giao diện vào/ra:

Bảng 1: Mô tả các tín hiệu vào ra của đơn vị sắp xếp.

3. Thuật toán sắp xếp

Bảng 2. Mã giả (Pseudo code) mô tả thuật toán.

| 1

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

— this algorithm is right for any K≥2

[initialize input data] Beginning: wait for start = ‘1’ Done = ‘0’ for i=0 to k-2 do A= Mi for j=i+1 to k-1 do B = Mj if A > B then Mi = B Mj = A A = Mi end if end for end for Done = ‘1’ wait for start = ‘0’ go to the beginning End |

Hình 3: Máy trạng thái FSMD mô tả thuật toán.

4. Kiến trúc RTL của mạch sắp xếp

4.1 Thiết kế mạch điện thực hiện chức năng xử lý dữ liệu trong đơn vị sắp xếp

Hình 4: Thiết kế Datapath.

4.2 Thiết kế máy trạng thái thực hiện chức năng điều khiển trong đơn vị sắp xếp

Hình 5: Máy trạng thái FSM.

5. Mô tả thiết kế bằng ngôn ngữ mô tả phần cứng VHDL

Down load mã nguồn VHDL ở đây. Hoặc liên hệ với tác giả theo địa chỉ email lsidesign1688@gmail.com để nhận mã nguồn VHDL.

Hình 7. Mã nguồn VHDL mô tả thiết kế bộ sắp xếp

Hình 7. Mã nguồn VHDL mô tả thiết kế bộ sắp xếp

6. Mô phỏng thiết kế với bộ mô phỏng ModelSim

Hình 8: Kết quả mô phỏng.

Phân tích kết quả mô phỏng:

Khung màu đỏ trong hình 8 chỉ ra chuỗi dữ liệu đầu vào gồm 4 phần tử có giá trị 3, 1, 4, 2. Sau thời gian sắp xếp ta có được chuỗi dữ liệu đầu ra gồm 4 phần tử tương ứng nhưng đã được sắp xếp theo trật tự tăng dần như chỉ ra trong khung màu xanh của Hình 8.

Quá trình sắp xếp được điều khiển bởi xung start bắt đầu từ thời điểm 460ns và kết thúc tại thời điểm 1612ns. Vì chu kì clock được thiết lập trong testbench là 20ns, nên tổng số chu kỳ được dùng để hoàn thành quá trình sắp xếp là (1600-460)/20 = 57 chu kỳ.