NỘI DUNG

Kiến trúc phần cứng có thể tái cấu hình cho các ứng dụng xử lý đa phương tiện

1. Vấn đề cần giải quyết

Như giới thiệu ở bàiCGRA: Mảng phần cứng có khả năng tái cấu hình cấu trúc thô, kỹ thuật tính toán có thể tái cấu hình được đề xuất nhằm lấp vào khoảng trống giữa phương pháp thực hiện bằng phần cứng chuyên dụng ASIC và phương pháp thực thi bằng phần mềm trên các bộ vi xử lý. Phương pháp này cho phép đạt được hiệu năng tính toán cao xấp xỉ sự thực hiện bằng ASIC trong khi duy trì được mức mềm dẻo giống như sự thực hiện bằng phần mềm trên vi xử lý. Phương pháp tái cấu hình thời gian chạy mở rộng ý tưởng về khả năng tái cấu hình bằng việc thêm vào khả năng thay đổi cấu trúc phần cứng không chỉ giữa các ứng dụng ở thời điểm cấp nguồn hoặc khởi động lại hệ thống mà còn giữa các phần khác nhau của cùng một ứng dụng khi hệ thống đang làm việc. Tuy nhiên trong nhiều tình huống thời gian dành cho tái cấu hình lại phần cứng có thể chiếm tới 98,5% tổng thời gian thực thi của ứng dụng [4]. Lượng thời gian tái cấu hình quá lớn như vậy có thể làm lu mờ đi lợi ích đạt được nhờ sự tăng tốc độ tính toán trên phần cứng, hậu quả là hiệu quả sử dụng hệ thống tái cầu hình bị suy giảm. Do đó, nó là cần thiết phải có một giải pháp tái cấu hình hiệu quả để giảm thời gian dùng cho tái cấu hình lại phần cứng.

Cấu trúc của phần cứng có thể tái cấu hình cũng có ảnh hưởng lớn tới phạm vi ứng dụng và thời gian tái cấu hình lại phần cứng. Dựa theo mức lõi hay kích thước nhỏ nhất của một đơn vị logic có thể tái cấu hình (tính theo số bit nhị phân), các kết cấu phần cứng có thể tái cấu hình có thể phân chia thành hai loại: kết cấu có mức lõi tinh (fine-grained granularity) và kết cấu có mức lõi thô (coarse-grained granularity).Được so sánh với với các cấu trúc lõi thô, cấu trúc lõi tinh như FPGA thường có tính mềm dẻo cao hơn và có phạm vi ứng dụng rộng hơn bởi khả năng xây dựng các cấu trúc phần cứng bất kỳ từ các phần tử logic cơ bản (thường là các bảng tra cứu LUT (Look-up Table) và các thanh ghi) mà nó cung cấp. Tuy nhiên, chính ưu điểm này của FPGA lại là nguyên nhân dẫn đến nhược điểm nghiêm trọng của nó: FPGA có công suất tiêu thụ, trễ đường truyền, diện tích thực thi rất lớn do nó đòi hỏi một lượng lớn các tài nguyên định tuyến cho việc xây dựng các mạch điện tử từ các phần tử lô-gic cơ bản. Hậu quả là, FPGA thường không phù hợp cho việc thực hiện các ứng dụng cho các thiết bị di động cầm tay. Các kết cấu có thể tái cấu hình lõi thô đạt được sự dung hòa tốt hơn giữa các đặc tính như tính mềm dẻo, hiệu năng, cũng như công suất tiêu thụ và diện tích. Các CGRA hiện nay thường được đề xuất nhằm khai thác cơ chế song song mức dữ liệu DLP (Data-Level Parallelism) và cơ chế song song mức lệnh ILP (Instruction-Level Parallelism) của một thuật toán. Một loại cơ chế song song khác là cơ chế song song mức tác vụ TLP (Task-Level Parallelism) cũng có thể được khai thác để tăng hiệu quả sử dụng các tài nguyên phần cứng có thể tái cấu hình.

2. Mục tiêu

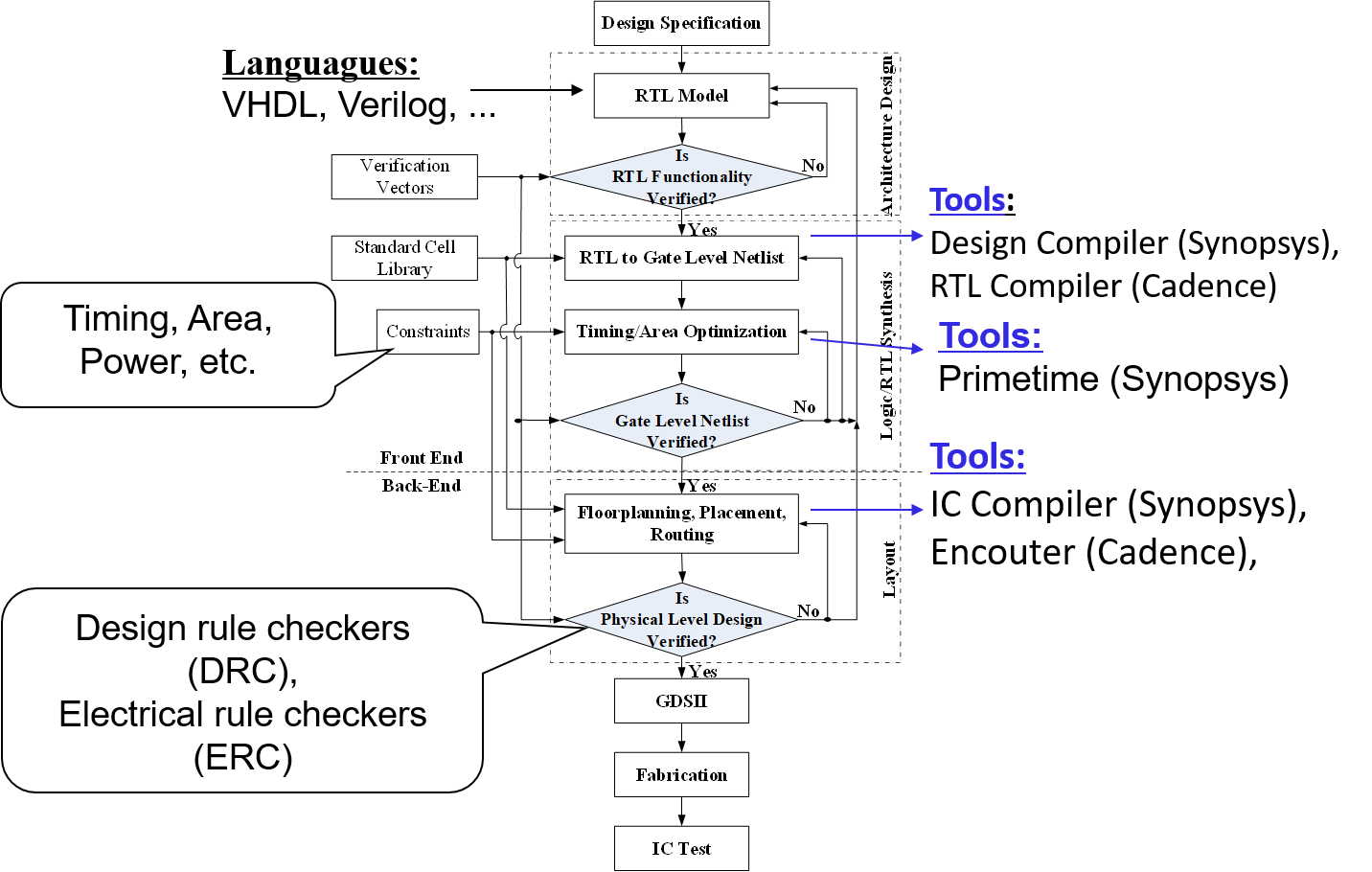

Mục tiêu nghiên cứu của đề tài là khảo sát các kiến trúc phần cứng có thể tái cấu hình hiện có, từ đó đề xuất và phát triển một kiến trúc mảng phần cứng có thể tái cấu hình lõi thô cho các ứng dụng xử lý đa phương tiện, ký hiệu là MUSRA (MUltimedia-Specified Reconfigurable Architecture). MUSRA nhắm tới mục tiêu tăng tốc độ tính toán cho các nhiệm vụ tính toán chuyên sâu bằng việc khai thác nhiều mức cơ chế song song như DLP (Data Level Parallelism), ILP (Instruction Level Parallelism), TLP (Task Parallelism) trong một thuật toán, đồng thời giải quyết được vấn đề về yêu cầu băng thông dữ liệu lớn và thời gian cấu hình lớn tồn tại trong các mảng tính toán CGRA nhằm tăng hiệu năng xử lý. Kiến trúc mảng phần cứng có thể tái cấu hình này sau đó cần được mô hình hóa ở mức cao (dùng ngôn ngữ C++ hoặc SystemC) và mức RTL (Register Transfer Level) (dùng ngôn ngữ mô tả phần cứng VHDL) để mô phỏng và phân tích hiệu năng của kiến trúc hệ thống mục tiêu, cũng như hỗ trợ khả năng đồng kiểm chứng phần cứng – phần mềm khi ánh xạ một ứng dụng benchmark lên hệ thống. Mô hình mức cao cũng là nền tảng quan trọng để xây dựng các công cụ cho phép phân chia phần cứng/phần mềm (Hardwarre/Software Partition) và ánh xạ tự động các thuật toán ứng dụng lên kiến trúc phần cứng có thể tái cấu hình đã đề xuất trong tương lai. Mô hình RTL phục vụ mục đích tổng hợp và thực thi kiểm thử kiến trúc được đề xuất trên nền tảng FPGA nhằm đánh giá hiệu năng, giá thành thực thi và ước lượng công suất tiêu thụ của hệ thống. Cuối cùng nó là cần thiết phải triển khai một hệ thống tích hợp trên chip SoC (System-on-Chip) nhằm mục đích kiểm chứng khả năng tái cấu hình linh hoạt và hiệu năng cao của kiến trúc với một tập hợp các ứng dụng benchmark trong lĩnh vực xử lý multimedia.

3. Phương pháp nghiên cứu

Để thực hiện được mục tiêu đề tài đặt ra, nhóm nghiên cứu đã tập trung nghiên cứu kỹ các vấn đề lý thuyết, thuật toán và tình trạng triển khai thiết kế các hệ thống tính toán có thể tái cấu hình trên thế giới. Trong quá trình triển khai thực hiện đề tài, nhóm nghiên cứu đã khảo sát các vấn đề tới hạn liên quan đến kỹ thuật và công nghệ trong việc thực hiện các phần cứng có thể tái cấu hình, các kỹ thuật biên dịch cho việc ánh xạ một chương trình phần mềm lên phần cứng có thể tái cấu hình, phân tích các ứng dụng benchmark trong các ứng dụng đa phương tiện (multimedia) và xu thế phát triển của các hệ thống đa phương tiện thế hệ tiếp theo. Bên cạnh đó, các kỹ thuật tính toán hiệu năng cao như tính toán song song, kỹ thuật đường ống pipeline, các mô hình tính toán SIMD (Single Instruction, Multiple data), MIMD (Multiple Instruction, Multiple Data), VLIW (Very Long Instruction Word) v.v. cũng được phân tích và ứng dụng khi đề xuất thiết kế tổng thể của mảng MUSRA. Từ đó, kết hợp với yêu cầu đặt ra, nhóm nghiên cứu đã xây dựng bản đặc tả thiết kế và tiến hành đề xuất thiết kế cho mảng phần cứng có thể tái cấu hình đáp ứng các yêu cầu về tính năng cũng như khả năng cấu hình linh hoạt cho một dải các ứng dụng đa phương tiện thế hệ mới.

Trong phương pháp thực thi bằng phần cứng có thể tái cấu hình, một ứng dụng sẽ không hoàn toàn được thực hiện bằng phần cứng (giống như phương pháp ASIC) hoặc phần mềm (giống như phương pháp thực thi bằng vi xử lý) mà thường được thực thi đồng thời bằng cả phần cứng (một phần tính toán chuyên sâu của thuật được ánh xạ tới phần cứng có thể tái cấu hình) và cả phần mềm (chẳng hạn phần điều khiển của thuật toán chạy trên vi xử lý). Do đó, nhóm nghiên cứu cũng tiến hành khảo sát các vấn đề liên quan đến thiết kế mức hệ thống điện tử ESL (Electronic System Level) nhắm tới việc xây dựng các mô hình mức cao (bằng ngôn ngữ bậc cao như C/C++, VHDL) của hệ thống. Phần cứng tái cấu hình được mô hình hoá bằng các ngôn ngữ bậc cao sao cho cả các tác vụ phần cứng và tác vụ phần mềm của một thuật toán có thể được đồng thời mô phỏng khi đánh giá kiến trúc đề xuất với các ứng dụng benchmark. Hơn thế, mô hình mức cao này cũng phục vụ cho việc mô phỏng và phân tích các thông số khác nhau của kiến trúc hệ thống mục tiêu, hoặc xa hơn là để phát triển các công cụ biên dịch tự động các chương trình ứng dụng để tạo ra thông tin cấu hình cho MUSRA. Sau khi đã khẳng định tính khả thi của kiến trúc được đề xuất thông qua việc mô phỏng đánh giá với các mô hình mức cao, nhóm nghiên cứu đã tiến hành xây dựng mô hình mức RTL của kiến trúc được đề xuất. Đây là mô hình có thể tổng hợp thành phần cứng thực thi các chức năng của kiến trúc mảng tái cấu hình được đề xuất. Mô hình RTL được sử dụng cho mục đích đánh giá kiến trúc được đề xuất ở các khía cạnh về hiệu năng và công suất tiêu thụ. Kiến trúc được đề xuất sau đó cần được kiểm thực trên một môi trường vật lý như FPGA trước khi quyết định có được gửi đi chế tạo sản xuất hay không. Do đó, một hệ thống tích hợp SoC (System-on-Chip) đã được đề xuất và thực thi trên nền tảng FPGA của Xilinx nhắm tới mục tiêu kiểm thực mảng MUSRA với một số ứng dụng thực tế.

Pingback: MUSRA#7: Mã VHDL mức RTL bộ DMAC với chức năng sắp xếp một dãy số - SMART ELECTRONICs