NỘI DUNG

Design and Implementation of DMAC with a built-in Matrix Transposer

DOWNLOAD VHDL CODE HERE

1. Mục tiêu

Đề xuất thiết kế mức RTL, mô hình hóa bằng VHDL, mô phỏng bằng ModelSIM và thực thi một bộ điều khiển truy xuất bộ nhớ trực tiếp DMAC có khả năng chuyển vị ma trận (Matrix transposer). Đơn vị thực hiện chức năng copy một ma trận có kích thước R×C (R hàng C cột) từ địa chỉ A, thực hiện chuyển vị ma trận và sau đó ghi tới tới địa chỉ B trong không gian bộ nhớ của hệ thống. Các tham số R×C, A, B phải được nạp vào các thanh ghi (RIR, CIR), SAR và DAR của DMAC trước khi quá trình DMA diễn ra.

2. Yêu cầu

- Hỗ trợ giao thức ghép nối tới CPU theo chuẩn Intel bus interface

- Hỗ trợ giao thức ghép nối với mảng bộ nhớ của MUSRA

Bảng 1: Mô tả các tín hiệu vào ra.

| Signals | Direction | Width (bits) | Reset | Description |

| Generic | ||||

| DATA_WIDTH | 8 | N/A | Data Width | |

| ADDR_WIDTH | 8 | N/A | Address Width | |

| AIN_WIDTH | 4 | N/A | Ain Width | |

| Common Signals | ||||

| clk | Input | 1 | N/A | TÍn hiệu xung nhịp Clock |

| rst_n | Input | 1 | 0 | Tín hiệu Reset tích cực mức thấp |

| Configuration Port | ||||

| cs_n | Input | 1 | 1 | Tín hiệu chọn DMAC |

| iorin_n | Input | 1 | 1 | Tín hiệu clock cho phép đọc dữ liệu từ thanh ghi. |

| iowin_n | Input | 1 | 1 | Tín hiệu clock cho phép ghi dữ liệu từ dbin vào thanh ghi. |

| dreq | Input | 1 | 0 | Tín hiệu yêu cầu DMA |

| Hreq | Output | 1 | 0 | Tín hiệu yêu cầu CPU nhường quyền làm chủ bú |

| hlda | Input | 1 | 0 | Tín hiệu từ CPU xác nhận CPU từ bỏ quyển sử dụng BUS |

| dack | Output | 1 | 0 | Tín hiệu thông báo rằng DMA chuẩn bị truyền dữ liệu. |

| ain | Input | AIN_WIDTH | N/A | Tín hiệu địa chỉ chọn thanh ghi điều khiển của DMA. |

| dbin | Input | DATA_WIDTH | N/A | Dữ liệu cần nạp vào các thanh ghi điều khiển. |

| Ports for transferring data | ||||

| memr_n | Inout | 1 | 1 | Tín hiệu tích cực mức thấp cho phép đọc dữ liệu từ MEM vào DMAC. |

| memw_n | Inout | 1 | 1 | Tín hiệu tích cực mức thấp cho phép viết từ DMAC đến MEM. |

| addr_R | Input | ADDR_WIDTH | N/A | Địa chỉ cho đọc dữ liệu vào DMA. |

| data_i | Input | DATA_WIDTH | N/A | Cổng nhận dữ liệu vào DMAC |

| addr_W | Output | ADDR_WIDTH | N/A | Địa chỉ cho viết dữ liệu tới MEM. |

| data_o | Output | DATA_WIDTH | N/A | Cổng xuất dữ liệu ra khỏi DMAC |

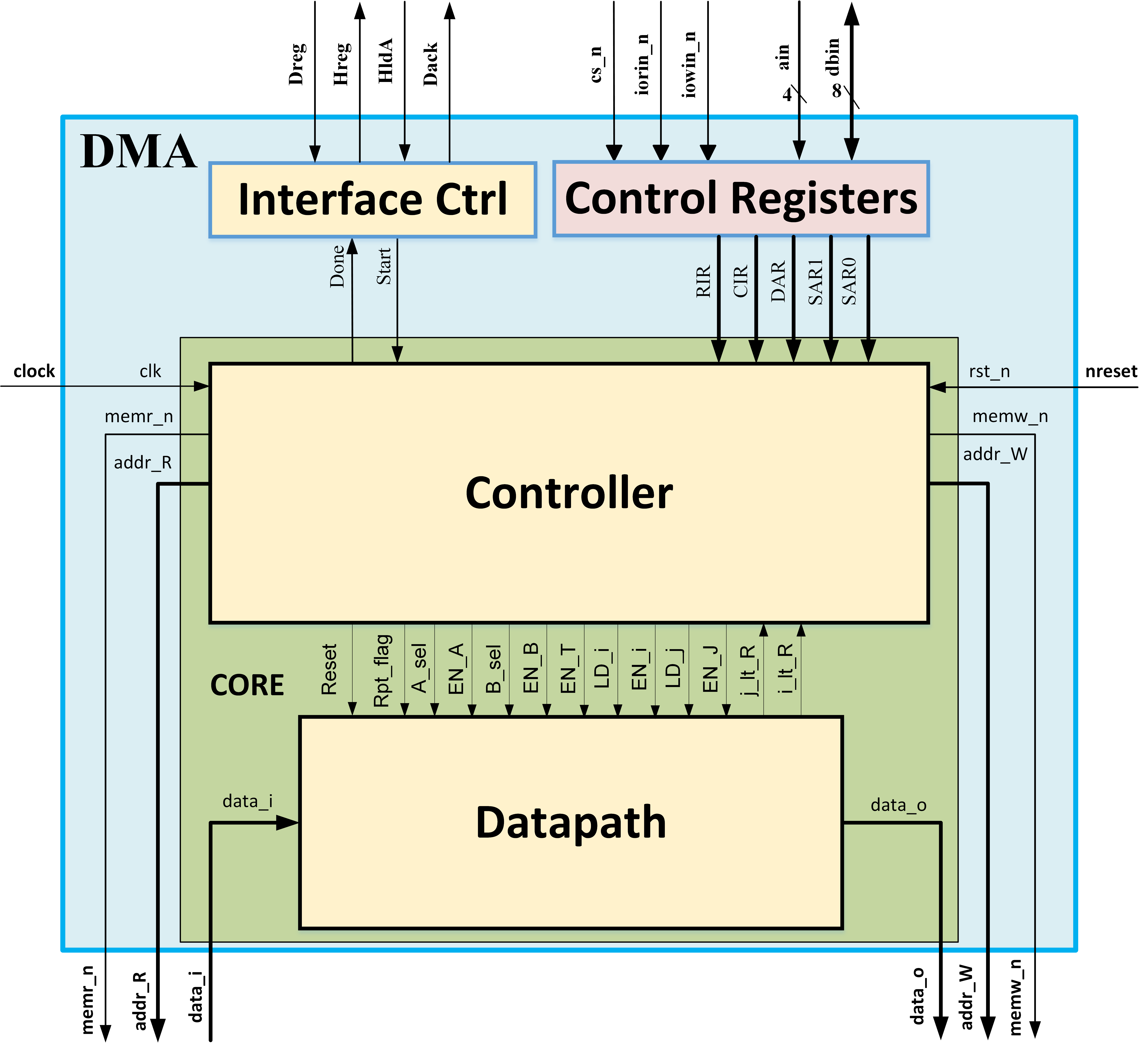

Matrix transposer là một đơn vị chức năng cho phép các thiết bị I/O có thể truy cập vào memory một cách độc lập với CPU giống như một bộ điều khiển truy xuất trực tiếp bộ nhớ DMAC. MATRIX TRANSPOSER thường có hai giao diện ghép nối:

- Giao diện ghép nối với CPU: Trong giao diện này CPU đóng vai trò thiết bị Master còn Matrix transposer là thiết bị Slave. Thông qua giao diện này CPU có thể viết các thông tin điều khiển vào Matrix transposer và giám sát trạng thái hoạt động của Matrix transposer.

- Giao diện giao tiếp với bộ nhớ và thiết bị ngoại vi: trong giao diện này Matrix transposer là thiết bị Master. Matrix transposer khởi phát việc đọc dữ liệu từ vị trí nguồn và ghi dữ liệu tới vị trí đích.

Để hỗ trợ cho việc trao đổi dữ liệu với thiết bị ngoại vi bằng cách truy cập trực tiếp vào bộ nhớ, CPU thường có một chân lối vào gọi là chân yêu cầu treo CPU (HOLD Request: Hreq) để thiết bị ngoại vi khi có yêu cầu dùng bus cho biệc trao đổi dữ liệu với bộ nhớ thì thông qua chân này mà báo cho CPU biết. Khi CPU nhận được yêu cầu treo thì nó tự tách ra khỏi hệ thống bus bằng cách đưa các chân kết nối của nó với bus vào trạng thái trở kháng cao và đưa xung HDLA ra ngoài để thông báo rằng CPU cho phép MATRIX TRANSPOSER được sử dụng bus đó.

Khi CPU tách ra khỏi hệ thống bằng việc tự treo để trao quyền sử dụng bus cho MATRIX TRANSPOSER, lúc này MATRIX TRANSPOSER chịu trách nhiệm điểu khiển toàn bộ hoạt động trao đổi dữ liệu của hệ thống. Để làm được điều đó MATRIX TRANSPOSER cần có các tín hiệu điều khiển cần thiết giống như các tín hiểu của CPU và nó phải lập trình được.

Quy trình hoạt động của MATRIX TRANSPOSER:

- Các thiết bị ngoại vi hoặc CPU yêu cầu truyền dữ liệu thông qua Matrix transposer bằng cách kéo chân dreq (DMA request) lên mức cao;

- MATRIX TRANSPOSER sẽ gửi tín hiệu hreq tới CPU, báo hiệu cho CPU rằng nó cần sử dụng đường bus dữ liệu và bus địa chỉ của hệ thống;

- CPU sẽ kết thúc chu trình sử dụng bus hiện tại và đáp ứng yêu cầu của MATRIX TRANSPOSER bằng cách đặt tín hiệu hlda lên mức cao để thông báo với MATRIX TRANSPOSER rằng nó có thể sử dụng các bus để thực hiện nhiệm vụ của mình. Tín hiệu hlda phải giữ ở mức cao khi MATRIX TRANSPOSER đang thực hiện nhiệm vụ.

- MATRIX TRANSPOSER sẽ đặt dack = ‘1’ để báo cho thiết bị ngoại vi biết rằng nó bắt đầu truyền dữ liệu.

- Khi DMAC bắt đầu truyền dữ liệu từ bộ nhớ sang ngoại vi hoặc từ bộ nhớ tới bộ nhớ bằng cách đặt địa chỉ của byte đầu tiên của khối cần truyền lên bus dữ liệu và kích hoạt memr_n để đọc dữ liệu của khối dữ liệu nguồn từ bộ nhớ vào bus dữ liệu. Tiếp theo nó kích hoạt memw_n để ghi dữ liệu vào bộ nhớ ở vị trí khối dữ liệu đích. Sau đó MATRIX TRANSPOSER giảm số từ cần gửi và tăng con trỏ địa chỉ, lặp laị quá trình này cho đến khi số đếm tiến tới 0 và kết thúc nhiệm vụ.

Sau khi MATRIX TRANSPOSER kết thúc công việc nó sẽ hủy kích hoạt hreq, báo hiệu với CPU rằng CPU có thể lấy lại quyền kiểm soát các đường bus.

3. Thuật toán chuyển vị một ma trận

Gọi b là chuyển vị của mảng a, ta có: b[j][i] = a[i][j] với i=0:R-1, j=0:C-1

Vì tổ chức vật lý của bộ nhớ là tuần tự và có thể mô hình hóa bằng mảng một chiều M[addr], nên: Nếu mảng a được lưu trong bộ nhớ M bắt đầu tại địa chỉ A thì: a[i][j] = M[A+i*C+j].

Quá trình chuyển vị một ma trận được mô tả bằng thuật toán như trong bảng dưới:

| Thuật toán 4: | |

| 1

2 3 4 5 6 7 8 9 10 11 12 13 14 |

–Variable addr_a, addr_b, I, j, T: 16-bit IntegerAddr_a := A;

for i= 0 to R-1 do { Addr_b := B+i; for j=0 to C-1 do { T := M[Addr_a] ; // đọc mảng a[][] và lưu vào biến T M[Addr_b] := T; // ghi giá trị của T vào mảng b Addr_a++; //tăng địa chỉ mảng a[][] lên 1 đơn vị để trỏ tới phần tử cột tiếp theo Addr_b +=R; // tăng địa chỉ mảng b để chuyển sang hàng tiếp theo } Addr_a ++; // tăng địa chỉ mảng a[][] lên 1 đơn vị để chuyển sang hàng tiếp theo } |

4. Thiết kế kiến trúc RTL

4.1 Giao diện ghép nối với CPU (Interface Ctrl)

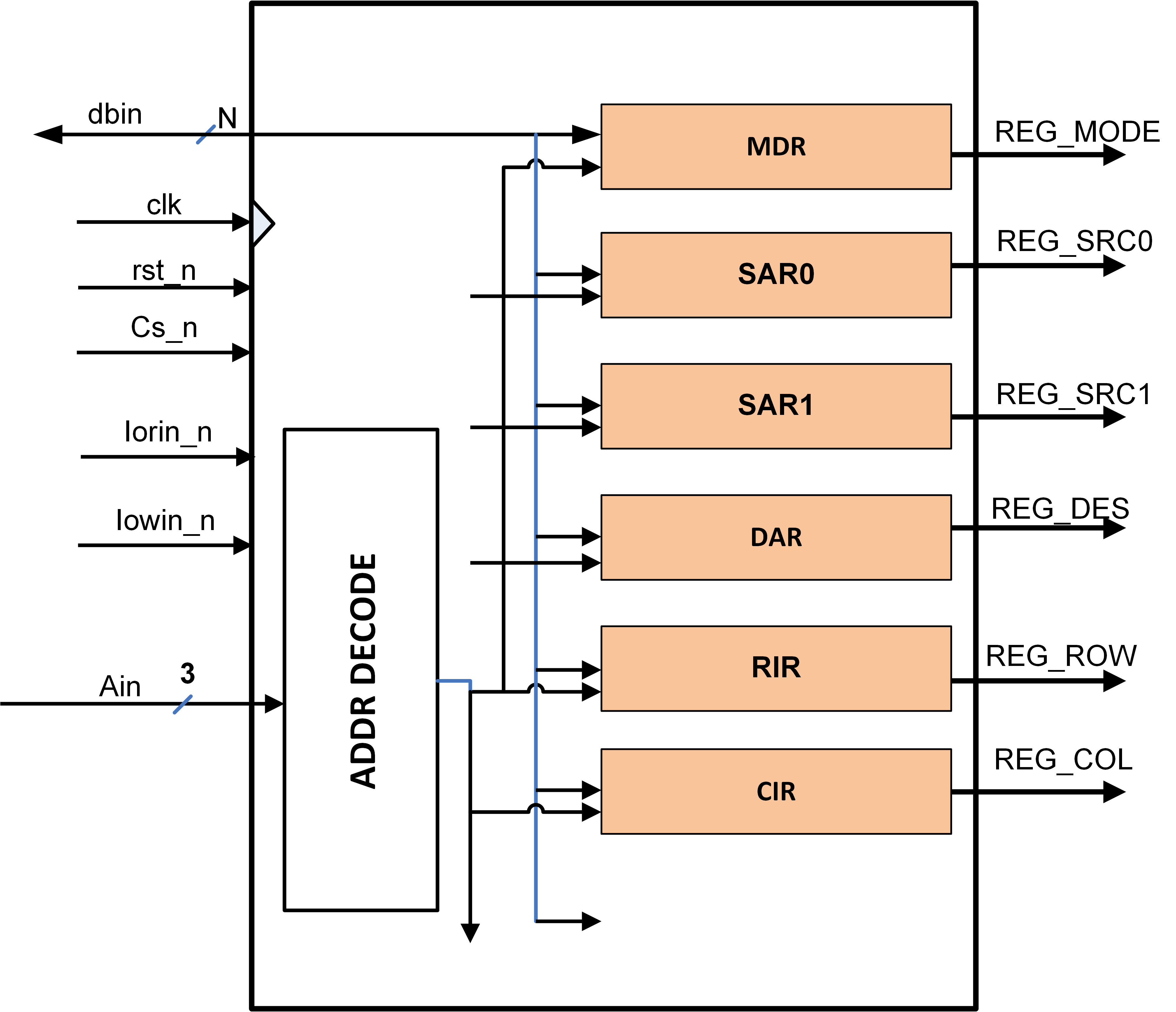

4.2 Các thanh ghi điều khiển

Tệp các thanh ghi điều khiển bao gồm 6 thanh ghi 8-bit lưu trữ các giá trị thiết lập chế độ làm việc của DMAC. Các thanh ghi trong tệp thanh ghi có thể được truy xuất đọc/viết từ bên ngoài (chẳng hạn CPU) thông quan giao diện ghép nối được chỉ ra bên cạnh trái của sơ đồ trong Hình 3. Trong khi đó các tín hiệu bên lề phải là giao diện ghép nối với đơn vị CCG của DMAC.

Bộ giải mã địa chỉ ADDR_DECODE trong tệp thanh ghi điều khiển nhận dữ liệu đầu vào từ bus Ain và lựa chọn một thanh ghi để viết dữ liệu như thể hiện trong Bảng 3.

Bảng 3: Các thanh ghi được lựa chọn theo giá trị của bus Ain.

| AIN | Thanh ghi được lựa chọn |

| “0000” | Thanh ghi MDR |

| “0001” | Thanh ghi SAR0 |

| “0010” | Thanh ghi SRA1 |

| “0011” | Thanh ghi DAR |

| “0100” | Thanh ghi RIR |

| “0101” | Thanh ghi CIR |

| “0110” |

Trong đó các thanh ghi được định nghĩa như sau:

- Thanh ghi chọn chế độ làm việc 8-bit MDR (MoDe Register). Thanh ghi này lựa chọn chế độ hoạt động của bộ điều khiển bộ nhớ. Bộ điều khiển đọc dữ liệu từ thanh ghi MDR và lựa chọn chế độ hoạt động thích hợp như chỉ ra trong Bảng 4.

Bảng 4: Chức năng hoạt động của bộ điều khiển bộ nhớ theo thanh ghi MDR[3:0].

| MDR[3:0] | Chức năng hoạt động |

| “0001” | Truy cập bộ nhớ trực tiếp |

| “0010” | Chuyển vị ma trận |

| “0100” | Sắp xếp mảng dữ liệu |

| “1000” | Ghép hai ma trận |

Bảng 5: Chức năng hoạt động của bộ điều khiển bộ nhớ theo thanh ghi MDR[4].

| MDR[4] | Chức năng hoạt động |

| ‘0’ | Single transfer mode: đọc/viết từng từ dữ liệu |

| ‘1’ | Burst transfer mode: đọc/viết theo loạt |

Bảng 6: Chức năng hoạt động của bộ điều khiển bộ nhớ theo thanh ghi MDR[5].

| MDR[5] | Chức năng hoạt động |

| ‘0’ | Data Width = 8 |

| ‘1’ | Data Width = 16 |

- Thanh ghi địa chỉ khối dữ liệu nguồn: SAR0 và SAR1 16-bit (Source Address Register). Các thanh ghi này lưu giá trị địa chỉ bắt đầu của các khối dữ liệu trong bộ nhớ mà DMAC cần phải truy xuất tới. Thông tin từ các thanh ghi SAR0 và SAR1 được sử dụng để tính toán địa chỉ cho việc đọc dữ liệu từ bộ nhớ.

- Thanh ghi địa chỉ đích: DAR 16-bit (Destination Address Register). Các thanh ghi này lưu giá trị địa chỉ bắt đầu của các khối dữ liệu trong bộ nhớ mà DMAC cần phải truy xuất tới. Thông tin từ thanh ghi DAR sử dụng để để tính toán địa chỉ cho việc ghi dữ liệu vào bộ nhớ.

- Thanh ghi độ dài khối dữ liệu: BLR 16-bit (Block Length Register). Thanh ghi BLR chứa thông tin về số lượng đơn vị dữ liệu cần xử lý. Thanh ghi này được tách thành 2 thanh ghi 8-bit có thể định địa chỉ một cách tách biệt: thanh ghi RIR (Row Index Register) chỉ số hàng của khối dữ liệu; thanh ghi CIR (Column Index Register) lưu số cột của khối dữ liệu. RIR tương ứng với 8-bit cao của BLR, CIR tương ứng với 8-bit thấp của BLR. Nói cách khác BLR = {RIR:CIR}.

- Nếu RIR !=0 thì RIR chỉ số hàng của khối dữ liệu cần copy

- Nếu RIR = 0 thì số hàng của khối dữ liệu cần copy là không xác định, tương ứng với vòng lặp vô hạn

4.3 Kiến trúc lõi DMAC

4.3.1 Datapath

4.3.2 Controller

5. Mã VHDL mô hình hóa thiết kế

DOWNLOAD MÃ NGUỒN VHDL Ở ĐÂY.

Mã nguồn VHDL mô tả thiết kế của DMAC được lưu trong thư mục RTL. Tổ chức top-down của các tệp mã nguồn được mô tả trong Hình 7.

6. Mô phỏng bằng ModelSIM

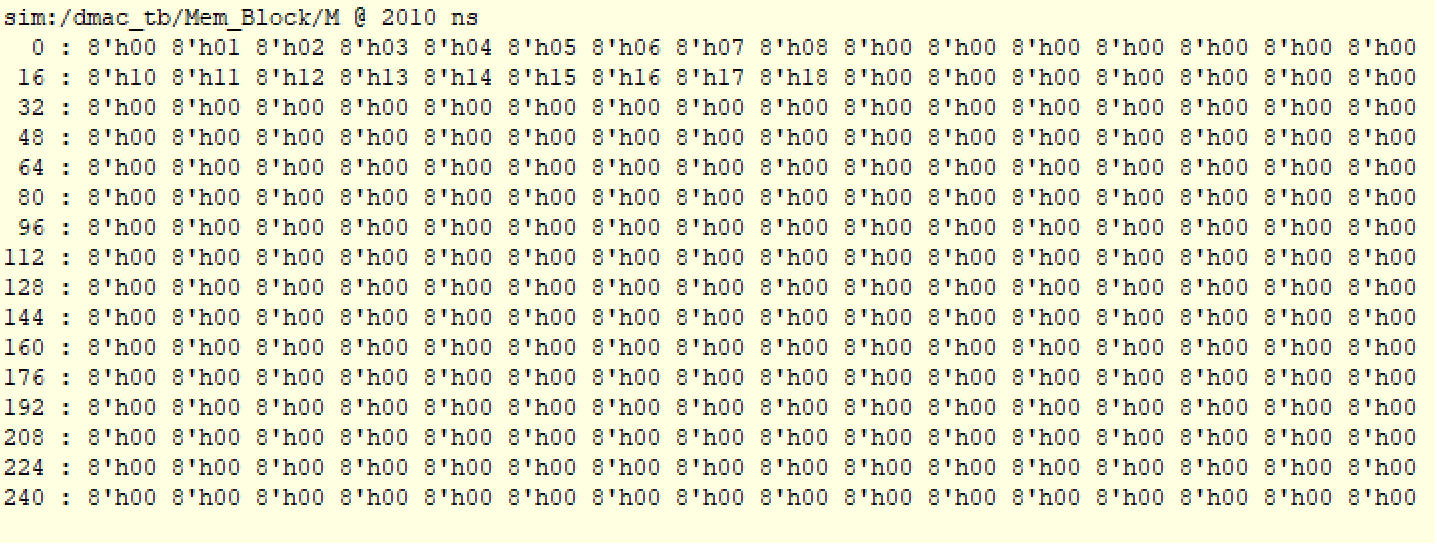

Mô hình hệ thống để mô phỏng kiểm chứng bộ DMAC chuyển vị ma trận được mô tả trong Hình 8. Bên cạnh bản mô tả mức RTL của DMAC, mô hình mô phỏng còn đưa vào 2 mô hình mức behavior của CPU và bộ nhớ, để tạo nên một hệ vi xử lý hoàn chỉnh.

Các hình bên dưới chỉ ra kết quả mô phỏng thiết kế Matrix transposer thực hiện việc copy ma trận A được lưu ở địa chỉ 0, sau đó chuyển vị và lưu thành ma trận B ở vị trí địa chỉ 32:

- Input: A = {0, 1, 2; 3, 4, 5; 6, 7, 8}.

- Output: B = {0, 3, 6; 1, 4, 7; 2, 5, 8}

Phân tích kết quả mô phỏng:

Kết quả mô phỏng cho thấy, thời gian để thực hiện chuyển vị một ma trận kích thước R×C tính từ thời điểm tín hiệu Dack chuyển tiếp lên 1 (báo hiệu bắt đầu quá trình chuyển vị ma trận) đến khi Dack chuyển tiếp về 0 (báo hiệu kết thúc quá trình chuyển vị ma trận) được tính bằng công thức:

T = (5C + 5)*R + 3.

(Nếu thêm 2 chu kì kiểm tra trạng thái sẵn sàng của bộ nhớ thì T = (7C + 5)*R + 3.

Xem video quá trình mô phỏng ở đây.

7. Kết quả tổng hợp phần cứng bằng Synopsys DC

Mô hình RTL của Matrix transposer đã được tổng hợp thành phần cứng bằng công cụ Synopsys Design compiler với thư viện công nghệ NANGATE 45nm open cell library. Kích thước thực thi của matrix transposer là khoảng 1.070,92µm2. Tần số hoạt động tối đa của mạch là khoảng 675MHz.